16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 产品特性

单 1.8V 电源供电

信噪比(SNR):

83dBFS(5MHz Fin、20MSPS)

无杂散动态范围(SFDR):

99dBFS(5MHz Fin、20MSPS)

采样频率可以低至 1MSPS

串行 LVDS 输出: 每个通道 1 位或 2 位

并口及 SPI 串口配置模式

52 引脚 (7mm×8mm) QFN 封装

支持内置或外置参考电压源

## 应用

通信

便携式医学成像

多通道数据采集

无损测试

## 产品聚焦

1. 管脚兼容 ADI 公司 LTC2271 系列

2. 统一的 1.8V 电源电压

3. 串行 LVDS 输出, 每通道 1 位或 2 位

4. 并口及串口配置支持 1.8V~3.6V 电平

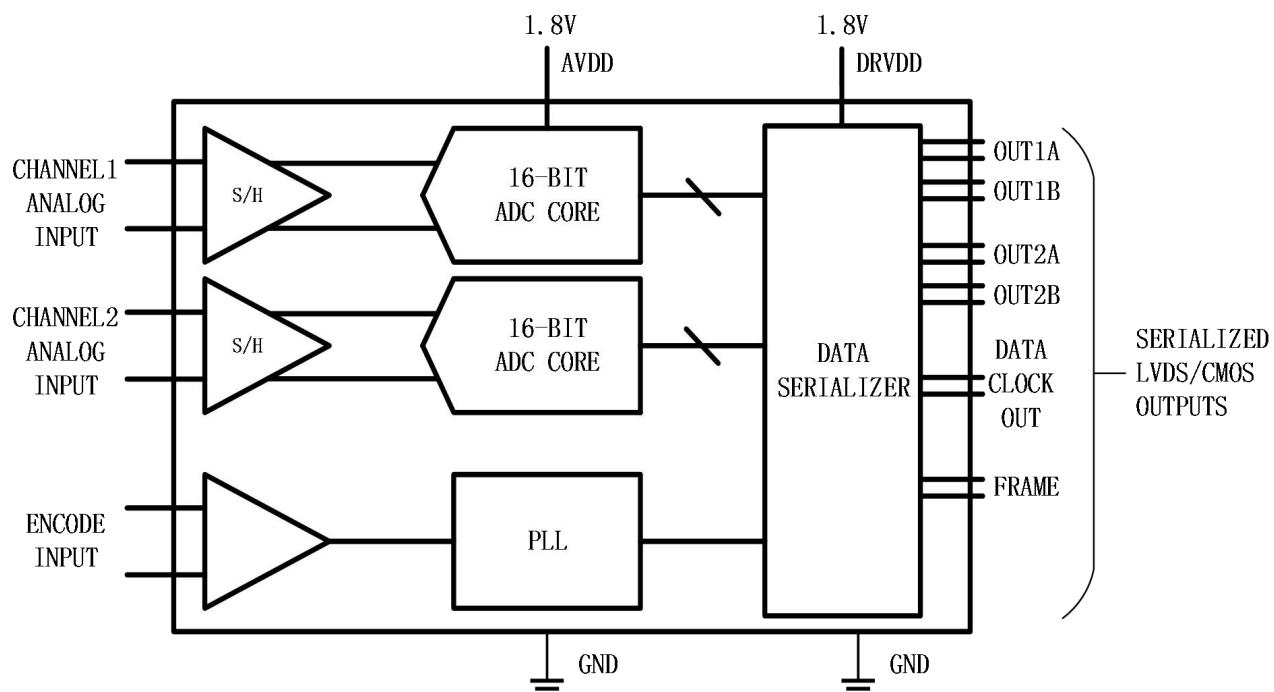

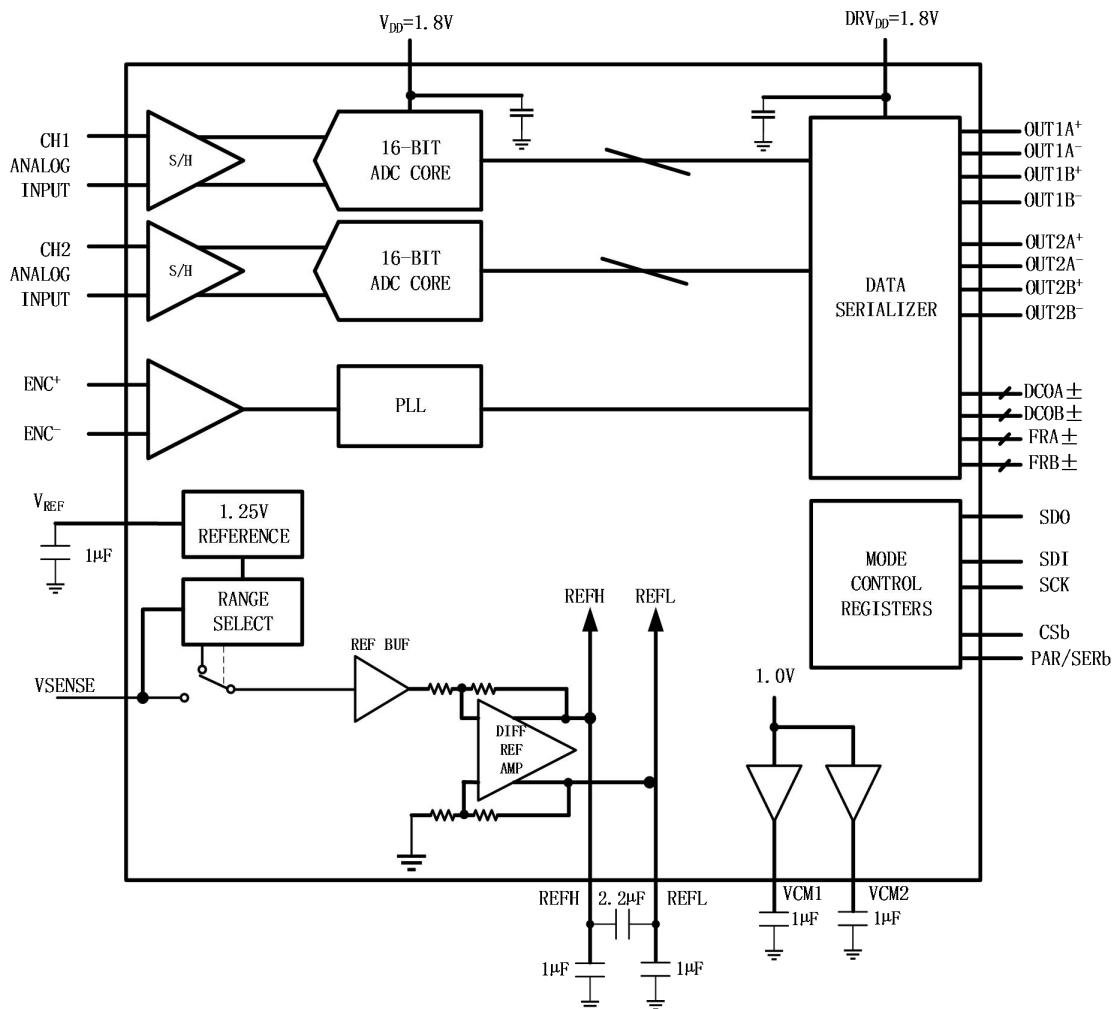

## 功能框图

图 1 功能框图

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 修订历史 (内部)

| 版本   | 时间         | 作者 | 修订内容           | 位置      |

|------|------------|----|----------------|---------|

| V1.0 | 2021/06/09 |    | 手册初稿           |         |

| V1.1 | 2021/8/23  |    | 补充测试数据         |         |

| V1.2 | 2021/8/23  |    | 修改页眉           |         |

| V1.3 | 2021/9/23  |    | 更新测试数据         |         |

| V1.4 | 2021/12/27 |    | 更新 test_mode   | P30,P31 |

| V1.5 | 2022/1/28  |    | 修改数字时序         | P9,P10  |

| V1.6 | 2022/2/28  |    | 增加 INL 图片      | P17     |

| V1.7 | 2022/3/15  |    | 更新 test_mode   | P30,P31 |

| V1.8 | 2022/3/28  |    | 修改 CMOS 输出描述符号 | P8      |

|      |            |    |                |         |

|      |            |    |                |         |

|      |            |    |                |         |

|      |            |    |                |         |

|      |            |    |                |         |

|      |            |    |                |         |

|      |            |    |                |         |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

# 目录

|                   |    |

|-------------------|----|

| 产品特性 .....        | 1  |

| 应用 .....          | 1  |

| 产品聚焦 .....        | 1  |

| 功能框图 .....        | 1  |

| 修订历史（内部） .....    | 2  |

| 目录 .....          | 3  |

| 概述 .....          | 4  |

| 技术规格 .....        | 5  |

| ADC 直流规格 .....    | 5  |

| ADC 交流规格 .....    | 6  |

| 数字规格 .....        | 7  |

| 时序规格 .....        | 8  |

| 时序图 .....         | 9  |

| 绝对最大额定值 .....     | 11 |

| 热特性 .....         | 11 |

| ESD 警告 .....      | 11 |

| 引脚配置和功能描述 .....   | 12 |

| 典型工作特性 .....      | 15 |

| 等效电路 .....        | 20 |

| 应用信息 .....        | 20 |

| 转换器工作 .....       | 20 |

| 模拟输入 .....        | 21 |

| 输入滤波 .....        | 21 |

| 变压器耦合电路 .....     | 21 |

| 放大器电路 .....       | 22 |

| 参考电平 .....        | 22 |

| REFH, REFL .....  | 22 |

| 时钟输入 .....        | 22 |

| 数字数据输出 .....      | 24 |

| 采样频率配置 .....      | 24 |

| 输出数据格式 .....      | 24 |

| 器件编程模式 .....      | 24 |

| 并行编程模式 .....      | 25 |

| 输出测试模式 .....      | 25 |

| 输出停用 .....        | 25 |

| 串行端口接口（SPI） ..... | 25 |

| 使用 SPI 的配置 .....  | 26 |

| 使用 SPI 的时序 .....  | 26 |

| 存储器映射 .....       | 28 |

| 存储器映射寄存器表 .....   | 28 |

| 应用信息 .....        | 34 |

| 设计指南 .....        | 34 |

| 外形尺寸 .....        | 35 |

| 名词对照表 .....       | 36 |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 概述

ZYL2271 是一款双通道、16 位 20MSPS 低噪声模数转换器（ADC），旨在支持需要高性能、低噪声、低成本、小尺寸、多功能的数据采集和通信应用。

这款双通道 ADC 内核采用差分、多级流水线结构，集成了输出纠错逻辑，集成内置基准源，支持引入外置基准源作为 ADC 的基准电压。

ADC 输出数据可以直接送至两个外部串行 LVDS 接口，每个通道可配置一次输出一位或两位，同时兼容支持串行 CMOS 输出(未开放)，可以最大程度降低功耗，满足便携设备更低功耗的需求。

设置与控制的编程利用四线式 SPI 兼容型串行接口来完成。

ZYL2271 采用 52 引脚 QFN 封装，额定温度为-40°C 至 85°C 工业温度范围。

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 技术规格

### ADC 直流规格

除非另有说明, AVDD=1.8V, DRVDD=1.8V, 采样率 20MHz, VIN=-1.0dBFS 差分输入, 2Vpp 输入范围。

表 1.

|                                                    |            |     | ZYL2271 |     |         |

|----------------------------------------------------|------------|-----|---------|-----|---------|

| 参数                                                 | 温度         | 最小值 | 典型值     | 最大值 | 单位      |

| 分辨率                                                | -40°C~85°C |     | 16      |     | 位       |

| 精度                                                 |            |     |         |     |         |

| 失调误差                                               | -40°C~85°C |     | ±1      |     | mV      |

| 增益误差                                               | -40°C~85°C |     | ±3      |     | %FS     |

| 失调匹配                                               |            |     | ±1      |     | mV      |

| 增益匹配                                               |            |     | ±0.1    |     | %FS     |

| 微分非线性 (DNL)                                        | 25°C       |     | ±1      |     | LSB     |

| 积分非线性 (INL)                                        | 25°C       |     | ±1      |     | LSB     |

| 温度漂移                                               |            |     |         |     |         |

| 失调误差                                               |            |     | ±20     |     | uV/°C   |

| 转换噪声 (transition noise)                            |            |     |         |     |         |

|                                                    | 25°C       |     | 1.43    |     | LSB rms |

| 模拟输入                                               |            |     |         |     |         |

| 输入范围 (ZYL2271-16)                                  |            |     | 2       |     | Vpp     |

| 输入共模电压                                             |            |     | 1       |     | V       |

| 模拟输入共模电流                                           |            |     | 100     |     | μA      |

| 模拟输入泄露电流<br>(不包括 Encode)                           |            | -1  |         | 1   | μA      |

| PAR/SERb 输入泄露电流                                    |            | -3  |         | 3   | μA      |

| 内部参考                                               |            |     |         |     |         |

| 共模输出电压                                             |            |     | 1.0     |     | V       |

| 共模输出电阻                                             |            |     | 150     |     | Ω       |

| 电源                                                 |            |     |         |     |         |

| 电源电压                                               |            |     |         |     |         |

| AVDD                                               | -40°C~85°C | 1.7 | 1.8     | 1.9 | V       |

| DRVDD                                              | -40°C~85°C | 1.7 | 1.8     | 1.9 | V       |

| 电源电流                                               |            |     |         |     |         |

| IAVDD                                              | 25°C       |     | 85.6    |     | mA      |

| IDRVDD (1.8V 2lane-CMOS)                           | 25°C       |     | 待测      |     | mA      |

| IDRVDD (1.8V 2lane-LVDS)                           | 25°C       |     | 40      |     | mA      |

| 功耗                                                 |            |     |         |     |         |

| 正弦波输入 <sup>1</sup> (DRVDD=1.8V<br>2lane CMOS 输出模式) | 25°C       |     | 待测      |     | mW      |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

|                                                            |      |  |      |  |    |

|------------------------------------------------------------|------|--|------|--|----|

| 正弦波输入 <sup>1</sup> (DRVDD=1.8V<br>2-lane LVDS 1.75mA 输出模式) | 25°C |  | 208  |  | mW |

| 正弦波输入 <sup>1</sup> (DRVDD=1.8V<br>2-lane LVDS 3.5mA 输出模式)  | 25°C |  | 226  |  | mW |

| 休眠功耗                                                       | 25°C |  | 1.5  |  | mW |

| 差分时钟输入额外增加功耗                                               |      |  | 13.3 |  | mW |

注释：1. 测量条件为：低输入频率、满量程正弦波、每个输出位的负载约为 5pF，单端 clock 输入。

## ADC 交流规格

除非另有说明，AVDD=1.8V，DRVDD=1.8V，采样率 20Msps，VIN=-1.0dBFS 差分输入，2Vpp 输入范围。

表 2.

| 参数                      | 温度         | 最小值 | ZYL2271 | 最大值 | 单位   |

|-------------------------|------------|-----|---------|-----|------|

| 信噪比(SNR)                |            |     |         |     |      |

| f <sub>IN</sub> =5MHz   | 25°C       |     | 83      |     | dBFS |

|                         | -40°C~85°C | 82  |         |     | dBFS |

| 无杂散动态范围(SFDR)           |            |     |         |     |      |

| f <sub>IN</sub> =5MHz   | 25°C       |     | 99      |     | dBFs |

|                         | -40°C~85°C | 90  |         |     | dBFs |

| 串扰(crosstalk)           | 25°C       |     | -110    |     | dB   |

| 模拟输入带宽(Input Bandwidth) | 25°C       |     | 待测      |     | MHz  |

## 数字规格

除非另有说明, AVDD=1.8V, DRVDD=1.8V, 采样率 20Msps, VIN=-1.0dBFS 差分输入, 2Vpp 输入范围。

表 3.

| 参数                                                 | 条件                      | 最小值  | 典型值  | 最大值 | 单位  |

|----------------------------------------------------|-------------------------|------|------|-----|-----|

| <b>时钟输入(ENC+, ENC-)</b>                            |                         |      |      |     |     |

| 逻辑兼容                                               | CMOS/LVDS/LVPECL        |      |      |     |     |

| <b>差分时钟输入(ENC-未连接至 GND)</b>                        |                         |      |      |     |     |

| 差分输入电压( $V_{ID}$ )                                 |                         | 0.2  |      |     | V   |

| 内部共模偏置( $V_{ICM}$ )                                |                         |      | 1.2  |     | V   |

| 输入电压范围( $V_{IN}$ )                                 |                         | 0.2  |      | 3.6 | Vpp |

| 输入电容( $C_{IN}$ )                                   |                         |      | 3.5  |     | pF  |

| 输入电阻( $R_{IN}$ )                                   |                         |      | 10   |     | kΩ  |

| <b>单端时钟输入(ENC-连接至 GND)</b>                         |                         |      |      |     |     |

| 高电平输入电压( $V_{IH}$ )                                |                         | 1.2  |      |     | V   |

| 低电平输入电压( $V_{IL}$ )                                |                         |      |      | 0.6 | V   |

| 输入电压范围( $V_{IN}$ )                                 |                         | 0    |      | 1.8 | V   |

| 输入电容( $C_{IN}$ )                                   |                         |      | 3.5  |     | pF  |

| 输入电阻( $R_{IN}$ )                                   |                         |      | 30   |     | kΩ  |

| <b>逻辑输入(CSb、SDI、SCK 处于串行或并行编程模式。SD0 处于并行编程模式)</b>  |                         |      |      |     |     |

| 输入电压范围                                             | $V_{DD}=1.8V$           | 0    |      | 3.6 | V   |

| 高电平输入电压( $V_{IH}$ )                                | $V_{DD}=1.8V$           | 1.22 |      |     | V   |

| 低电平输入电压( $V_{IL}$ )                                | $V_{DD}=1.8V$           |      |      | 0.6 | V   |

| 输入电流( $I_{IN}$ )                                   | $V_{IN}=0V$ 至 3.6V      | -10  |      | 10  | μA  |

| 输入电容( $C_{IN}$ )                                   | 全                       |      | 3    |     | pF  |

| <b>SD0 输出(串行编程模式。漏极开路输出。如果采用 SD0, 需要 2kΩ 上拉电阻)</b> |                         |      |      |     |     |

| 至 GND 的逻辑低电平输出电阻( $R_{IL}$ )                       | $V_{DD}=1.8V, SD0=0V$   |      | 200  |     | Ω   |

| 逻辑高电平输出漏电流( $I_{OH}$ )                             | SD0=0V 至 3.6V           | -10  |      | 10  | μA  |

| 输出电容( $C_{OUT}$ )                                  |                         |      | 3    |     | pF  |

| <b>数字数据输出</b>                                      |                         |      |      |     |     |

| <b>LVDS 模式</b>                                     |                         |      |      |     |     |

| 差分输出电压( $V_{OD}$ ), ANSI 模式                        | 100Ω 差分负载,<br>3.5mA 模式  |      | 350  |     | mV  |

| 输出共模电压( $V_{OS}$ ), ANSI 模式                        | 100Ω 差分负载,<br>3.5mA 模式  |      | 1.25 |     | V   |

| 差分输出电压( $V_{OD}$ ), 小摆幅模式                          | 100Ω 差分负载,<br>1.75mA 模式 |      | 175  |     | mV  |

| 输出共模电压( $V_{OS}$ ), 小摆幅模式                          | 100Ω 差分负载,<br>1.75mA 模式 |      | 1.25 |     | V   |

| 片内终端电阻( $R_{TERM}$ )                               | 终端被使能,                  |      | 100  |     | Ω   |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

|                      |               |     |  |     |   |

|----------------------|---------------|-----|--|-----|---|

|                      | DRVDD=1.8V    |     |  |     |   |

| <b>CMOS 模式</b>       |               |     |  |     |   |

| 高电平输出电压 ( $V_{OH}$ ) | $V_{DD}=1.8V$ | 1.6 |  | 1.8 | V |

| 低电平输出电压 ( $V_{OL}$ ) | $V_{DD}=1.8V$ | 0   |  | 0.2 | V |

## 时序规格

除非另有说明, AVDD=1.8V, DRVDD=1.8V, 采样率 20Msps, VIN=-1.0dBFS 差分输入, 1.0V 内部基准电压。无特殊说明, 仅指  $T_A=25^\circ\text{C}$ 。

表 4.

|                                    |                                  | ZYL2271        |                             |                |        |

|------------------------------------|----------------------------------|----------------|-----------------------------|----------------|--------|

| 参数                                 | 条件                               | 最小值            | 典型值                         | 最大值            | 单位     |

| 时钟输入参数                             |                                  |                |                             |                |        |

| 输入时钟速率                             |                                  | 1              |                             | 20             | MHz    |

| 转换速率                               |                                  | 1              |                             | 20             | MSPS   |

| 时钟周期                               |                                  | 50             |                             | 1000           | ns     |

| 时钟占空比                              |                                  | 45             |                             | 55             | %      |

| 孔径延迟 ( $t_{AP}$ )                  |                                  |                | 1                           |                | ns     |

| 孔径抖动 ( $t_j$ )                     |                                  |                | 0.12                        |                | ps rms |

| 串行数据                               |                                  |                |                             |                |        |

| 串行数据比特周期 ( $t_{SER}$ )             | 双线道, 16-bit 串行<br>单线道, 16-bit 串行 |                | $1/(8*f_s)$<br>$1/(16*f_s)$ |                | s      |

| FR 到 DCO 的延迟 ( $t_{FRAME}$ )       |                                  | $0.35*t_{SER}$ | $0.5*t_{SER}$               | $0.65*t_{SER}$ | s      |

| DATA 到 DCO 的延迟 ( $t_{DATA}$ )      |                                  | $0.35*t_{SER}$ | $0.5*t_{SER}$               | $0.65*t_{SER}$ | s      |

| 数据传播延迟 ( $t_{PD}$ ) <sup>1,2</sup> |                                  |                | $2.5n + K*t_{SER}$          |                | s      |

| 输出上升时间 ( $t_r$ )                   |                                  |                | 0.17                        |                | ns     |

| 输出下降时间 ( $t_f$ )                   |                                  |                | 0.17                        |                | ns     |

| DCO 逐周期抖动                          |                                  |                | 待测                          |                | ns     |

| 流水线延迟                              |                                  |                | 7                           |                | 周期     |

<sup>1</sup>:  $t_{PD}$  的延时周期数 K 由寄存器 0x0107 决定, 默认为 K=0.5。

天津市滨海新区中新生态城中天大道 1620 号生态科技园启发大厦 11 层 102-3 室

电话: 010-82743488

第 8 页 共 36 页

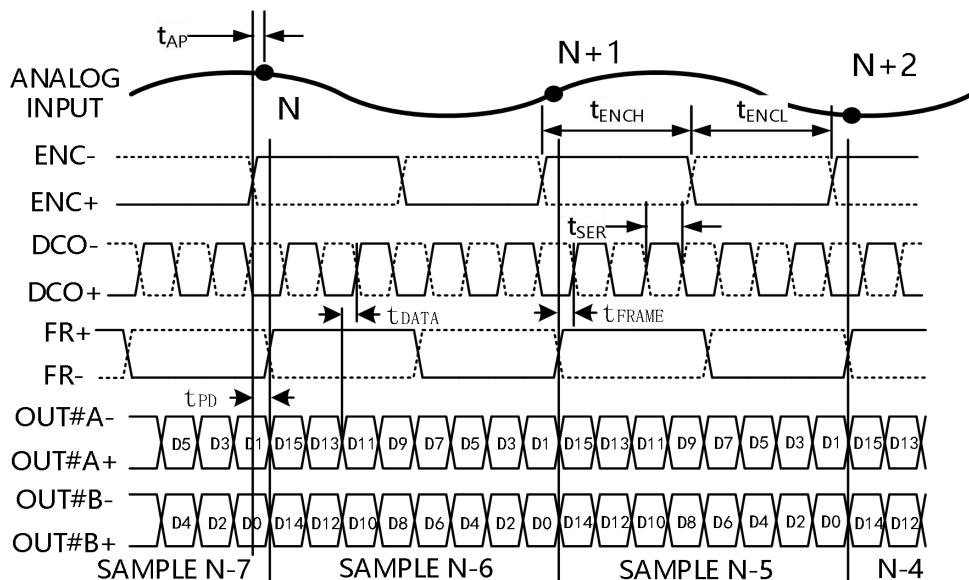

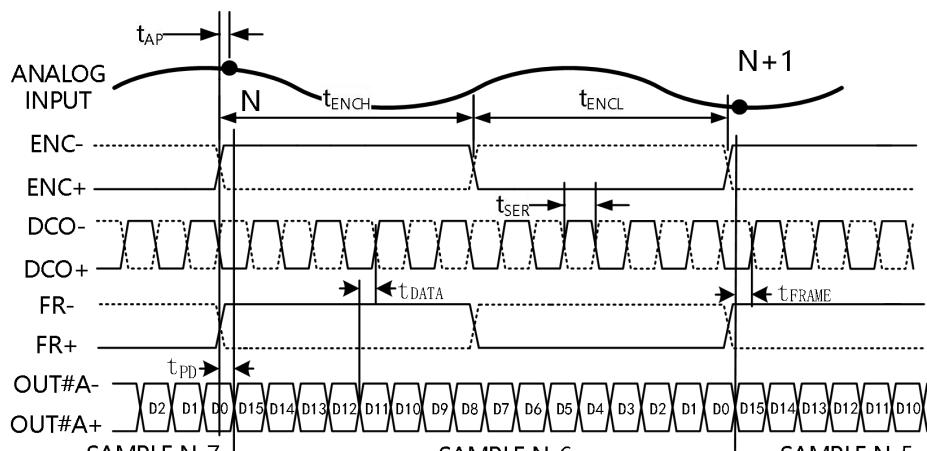

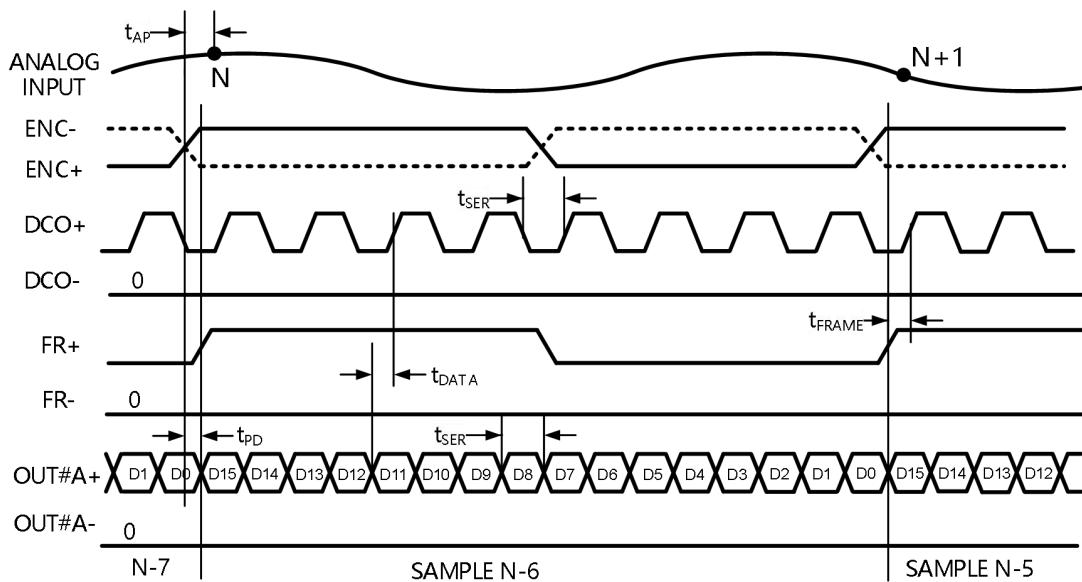

## 时序图

### 串行 LVDS 模式

图 2 数据输出时序——双线道 LVDS 输出模式, 16 位串行化

OUT#B+, OUT#B- ARE DISABLED

图 3 数据输出时序——单线道 LVDS 输出模式, 16 位串行化

16bit 20MSPS 1.8V双通道ADC

ZYL2271

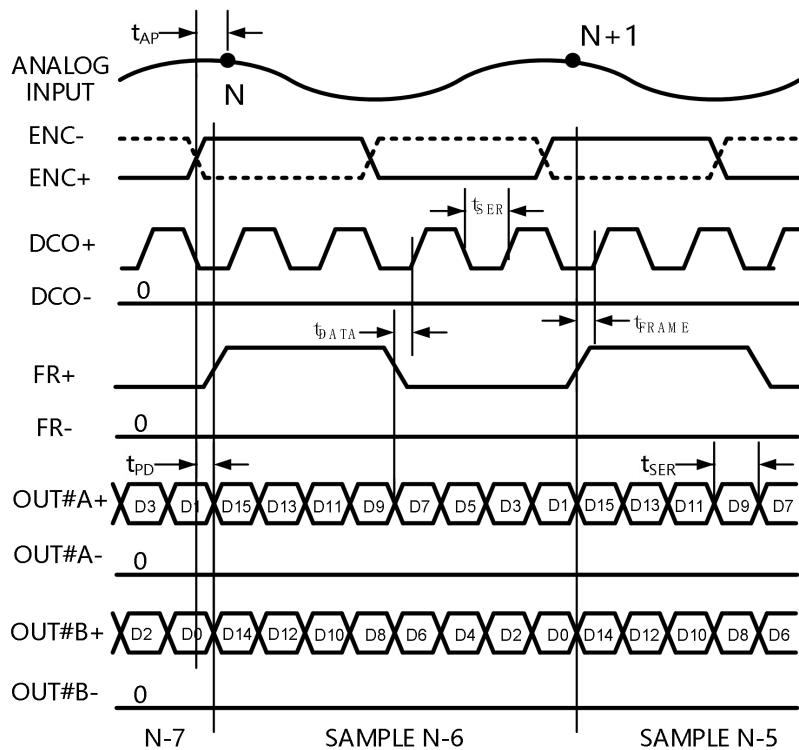

## 串行 CMOS 输出模式

图 4. 数据输出时序——双线道 CMOS 输出模式, 16 位串行化(未开放)

图 5. 数据输出时序——单线道 CMOS 输出模式, 16 位串行化(未开放)

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 绝对最大额定值

表 5.

| 参数                                                              | 额定值                           |

|-----------------------------------------------------------------|-------------------------------|

| 电器参数                                                            |                               |

| AVDD 至 GND                                                      | -0.3V~2.0V                    |

| DRVDD 至 GND                                                     | -0.3V~2.0V                    |

| AIN1+/AIN1-、AIN2+/AIN2-至 GND                                    | -0.3V~AV <sub>DD</sub> +0.2V  |

| ENC+、ENC-至 GND                                                  | -0.3V~2.0V                    |

| VREF 至 GND                                                      | -0.3V~2.0V                    |

| VCM 至 GND                                                       | -0.3V~2.0V                    |

| CSb 至 GND                                                       | -0.3V~3.9V                    |

| SCK 至 GND                                                       | -0.3V~3.9V                    |

| SDI 至 GND                                                       | -0.3V~3.9V                    |

| SDO 至 GND                                                       | -0.3V~3.9V                    |

| PAR/SERb 至 GND                                                  | -0.3V~3.9V                    |

| OUT1A+/OUT1A-, OUT1B+/OUT1B-, OUT2A+/OUT2A-, OUT2B+/OUT2B-至 GND | -0.3V~DRV <sub>DD</sub> +0.3V |

| DCO+/DCO-至 GND                                                  | -0.3V~DRV <sub>DD</sub> +0.3V |

| FR+/FR-至 GND                                                    | -0.3V~DRV <sub>DD</sub> +0.3V |

| 环境参数                                                            |                               |

| 工作温度范围 (环境)                                                     | -40°C~+85°C                   |

| 最大结温                                                            | 125°C                         |

| 存储温度范围 (环境)                                                     | -65°C~+150°C                  |

<sup>1</sup> 输入和输出的额定工作电压为电源电压 (AVDD 或 DRVDD) +0.2V, 但不得超过 2.1V。

注意, 超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值, 不表示在这些条件下或者在任何其他超出本技术规范操作章节中所示规格的条件下, 器件能够正常工作。长期在绝对最大额定值条件下工作会影响期间的可靠性。

## 热特性

QFN 封装的裸露焊盘必须焊接到接地层。将裸露焊盘焊接到 PCB 上可提高焊接可靠性, 从而最大限度发挥封装的热性能。

$\theta_{JA}$  典型值的测试条件为带实接地层的四层 PCB。如表 6 所示, 气流可改善散热, 从而降低  $\theta_{JA}$ 。另外, 直接与封装引脚接触的金属, 包括金属走线、通孔、接地层、电源层, 可降低  $\theta_{JA}$ 。

表 6. 热阻

| 封装类型  | 气流速度<br>(m/s) | $\theta_{JA}^{1,2}$ | $\theta_{JC}^{1,3}$ | $\theta_{JB}^{1,4}$ | 单位   |

|-------|---------------|---------------------|---------------------|---------------------|------|

| QFN52 | 0             | 29                  |                     |                     | °C/W |

<sup>1</sup> 按照 JEDEC 51-7, 加上 JEDEC25-5 2S2P 测试板。

<sup>2</sup> 按照 JEDEC JESD51-2(静止空气)或 JEDEC JESD51-6(流动空气)。

<sup>3</sup> 按照 MIL-Std 883, 方法 1012.1。

<sup>4</sup> 按照 JEDEC JESD51-8(静止空气)。

## ESD 警告

|  |                                                                                                                                         |

|--|-----------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>ESD(静电放电)敏感器件。</b><br/>带电器件和电路板可能会在没有察觉的情况下放电。<br/>尽管本产品有专有保护电路, 但在遇到高能量 ESD 时, 器件可能会损坏。因此, 应当采取适当的 ESD 防范措施, 以避免器件性能下降或功能丧失。</p> |

|--|-----------------------------------------------------------------------------------------------------------------------------------------|

天津市滨海新区中新生态城中天大道 1620 号生态科技园启发大厦 11 层 102-3 室

电话: 010-82743488

第 11 页 共 36 页

16bit 20MSPS 1.8V双通道ADC

ZYL2271

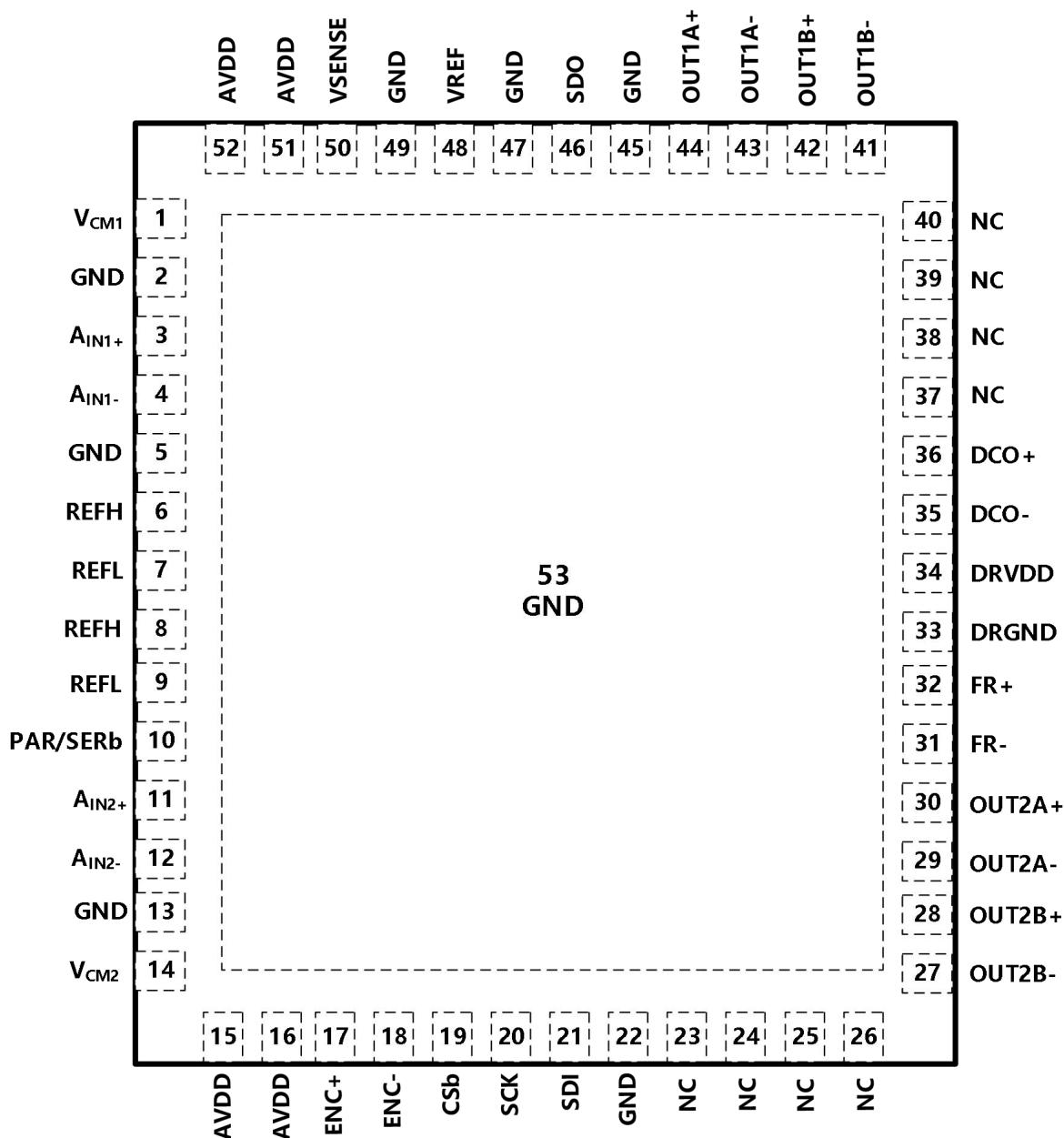

## 引脚配置和功能描述

图 6. 引脚配置

表 7. 引脚功能描述

| 引脚编号                                     | 引脚名称         | 类型    | 描述                                                                                    |

|------------------------------------------|--------------|-------|---------------------------------------------------------------------------------------|

| ADC 电源                                   |              |       |                                                                                       |

| 34                                       | DRVDD        | 电源    | 数字输出驱动器电源(标称值 1.8V)。                                                                  |

| 15, 16, 51, 52                           | AVDD         | 电源    | 模拟电源(标称值 1.8V)。                                                                       |

| 33                                       | DRGND        | 地     | 数字输出驱动器地。                                                                             |

| 2, 5, 13, 22, 45, 4<br>7, 49, 裸露焊盘<br>53 | GND,<br>裸露焊盘 | 地     | 封装底部的裸露热焊盘为器件提供模拟地。该焊盘必须与地相连, 才能正常工作。                                                 |

| ADC 模拟                                   |              |       |                                                                                       |

| 3                                        | AIN1+        | 输入    | 通道 1 的差分模拟输入引脚(+)。                                                                    |

| 4                                        | AIN1-        | 输入    | 通道 1 的差分模拟输入引脚(-)。                                                                    |

| 11                                       | AIN2+        | 输入    | 通道 2 的差分模拟输入引脚(+)。                                                                    |

| 12                                       | AIN2-        | 输入    | 通道 2 的差分模拟输入引脚(-)。                                                                    |

| 48                                       | VREF         | 输出    | 基准电压输出, 标准值 1.25V。用 1uF 电容去耦到地。                                                       |

| 6, 8                                     | REFH         | 输出    | ADC 高电平参考电压。去耦电容接法见“应用信息”的参考电压部分。                                                     |

| 7, 9                                     | REFL         | 输出    | ADC 低电平参考电压。去耦电容接法见“应用信息”的参考电压部分。                                                     |

| 50                                       | VSENSE       | 输入    | 接 AVDD, ADC 将选择内部基准和±1V 的输入范围。<br>接 1.2V~1.3V 之间的外部基准电压, ADC 将选择一个±0.8V*Vsense 的输入范围。 |

| 23, 24, 25, 26, 37<br>, 38, 39, 40       | NC           | 输入/输出 | 接去耦电容或悬空不连接, 差分布局可有可无。                                                                |

| 1                                        | VCM1         | 输出    | 通道 1 的模拟输入的共模电平偏置输出。                                                                  |

| 14                                       | VCM2         | 输出    | 通道 2 的模拟输入的共模电平偏置输出。                                                                  |

| 17                                       | ENC+         | 输入    | ADC 时钟输入(+)。                                                                          |

| 18                                       | ENC-         | 输入    | ADC 时钟输入(-)。                                                                          |

| 数字输出                                     |              |       |                                                                                       |

| 41                                       | OUT1B-       | 输出    | LVDS 模式: 通道 1 串行 LVDS 输出数据, 1 路模式下不使用。<br>CMOS 模式: 输出低电平。                             |

| 42                                       | OUT1B+       | 输出    | LVDS 模式: 通道 1 串行 LVDS 输出数据, 1 路模式下不使用。<br>CMOS 模式: 通道 1 串行 CMOS 输出数据, 1 路模式下不使用。      |

| 43                                       | OUT1A-       | 输出    | LVDS 模式: 通道 1 串行 LVDS 输出数据。<br>CMOS 模式: 输出低电平。                                        |

| 44                                       | OUT1A+       | 输出    | LVDS 模式: 通道 1 串行 LVDS 输出数据。<br>CMOS 模式: 通道 1 串行 CMOS 输出数据。                            |

| 27                                       | OUT2B-       | 输出    | LVDS 模式: 通道 2 串行 LVDS 输出数据, 1 路模式下                                                    |

|               |          |       |                                                                                                                                                                                              |

|---------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |          |       | 不使用。<br>CMOS 模式：输出低电平。                                                                                                                                                                       |

| 28            | OUT2B+   | 输出    | LVDS 模式：通道 2 串行 LVDS 输出数据，1 路模式下不使用。<br>CMOS 模式：通道 2 串行 CMOS 输出数据，1 路模式下不使用。                                                                                                                 |

| 29            | OUT2A-   | 输出    | LVDS 模式：通道 2 串行 LVDS 输出数据。<br>CMOS 模式：输出低电平。                                                                                                                                                 |

| 30            | OUT2A+   | 输出    | LVDS 模式：通道 2 串行 LVDS 输出数据。<br>CMOS 模式：通道 2 串行 CMOS 输出数据。                                                                                                                                     |

| 31            | FR-      | 输出    | LVDS 模式：数据帧开始标志位输出 (-)。<br>CMOS 模式：输出低电平。                                                                                                                                                    |

| 32            | FR+      | 输出    | LVDS 模式：数据帧开始标志位输出 (+)。<br>CMOS 模式：数据帧开始标志位输出 (+)。                                                                                                                                           |

| 35            | DCO-     | 输出    | LVDS 模式：LVDS 数据时钟输出 (-)。<br>CMOS 模式：输出低电平。                                                                                                                                                   |

| 36            | DCO+     | 输出    | LVDS 模式：LVDS 数据时钟输出 (+)。<br>CMOS 模式：CMOS 数据时钟输出 (+)。                                                                                                                                         |

| <b>SPI 控制</b> |          |       |                                                                                                                                                                                              |

| 20            | SCK      | 输入    | 在串行编程模式下，SPI 串行时钟/数据格式选择引脚。<br>在并行编程模式下，LVDS 输出电流选择控制信号，选择 3.5mA 或 1.75mA，可以被 1.8V 至 3.3V 逻辑控制。                                                                                              |

| 21            | SDI      | 输入    | 在串行编程模式下，SPI 串行数据输入引脚。<br>在并行编程模式下，芯片掉电模式控制信号，可以被 1.8V 至 3.3V 逻辑控制。                                                                                                                          |

| 19            | CSb      | 输入    | 在串行编程模式下，SPI 片选(低电平有效)<br>并行编程模式 2 路/1 路选择信号<br>0 = 2 路，16 位串行输出模式<br>1 = 1 路，16 位串行输出模式                                                                                                     |

| 46            | SDO      | 输出\输入 | 在串行编程模式下，SPI 串行数据输出引脚。SDO 是开漏 NMOS 输出，需要外部 $2k\Omega$ 上拉电阻到 1.8V 至 3.3V。在并行编程模式下，为 LVDS 数据输出引脚内部端接电阻使能控制信号。控制 LVDS 数据输出引脚是否接通内部 100ohm 端接电阻。作为输入信号时，可以被 1.8V 至 3.3V 逻辑控制，需要串联 $1k\Omega$ 电阻。 |

| <b>ADC 配置</b> |          |       |                                                                                                                                                                                              |

| 10            | PAR/SERb | 输入    | 编程模式选择引脚。接地时为串行编程模式，接 DRVDD 时为并行编程模式。该引脚应该直接接电源或地，不要被逻辑信号驱动。                                                                                                                                 |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

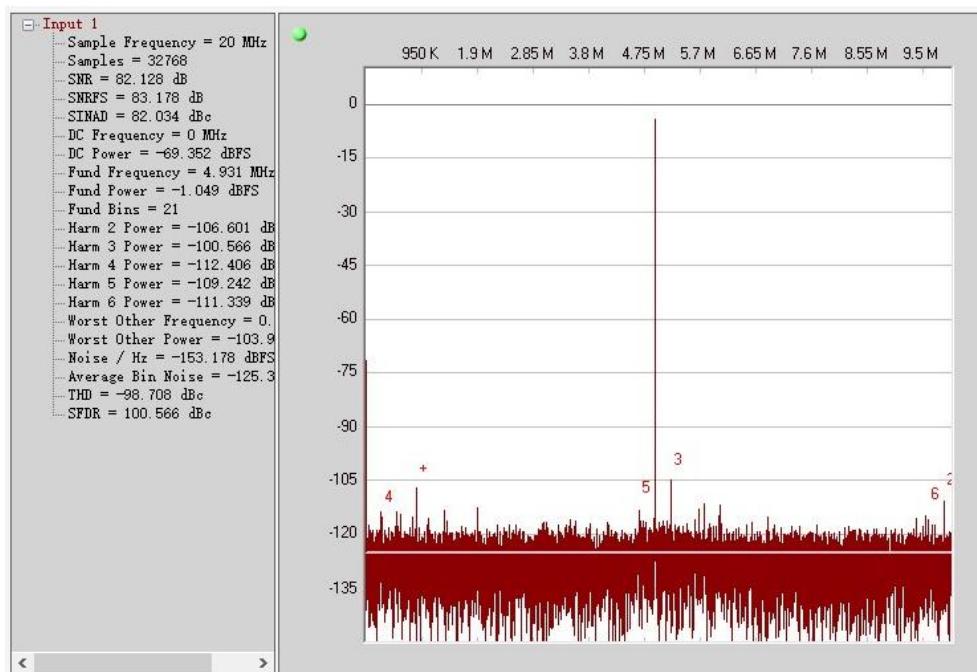

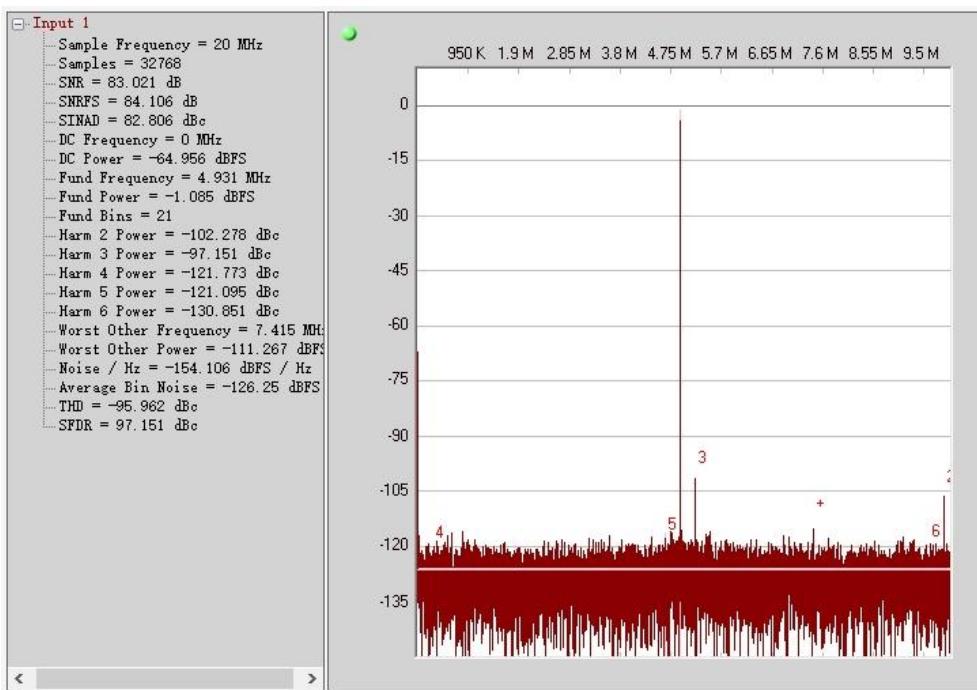

## 典型工作特性

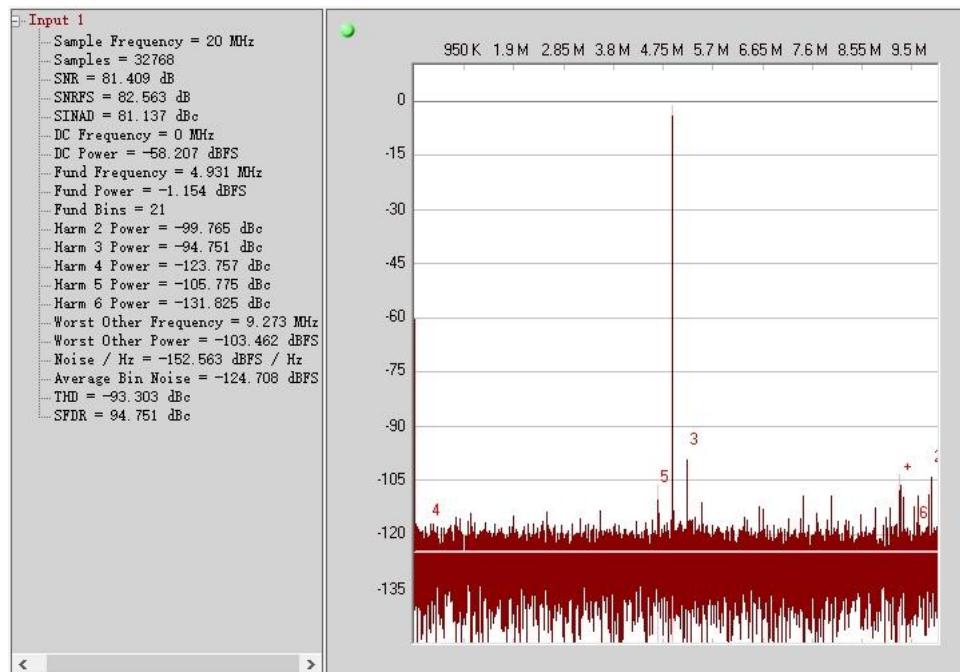

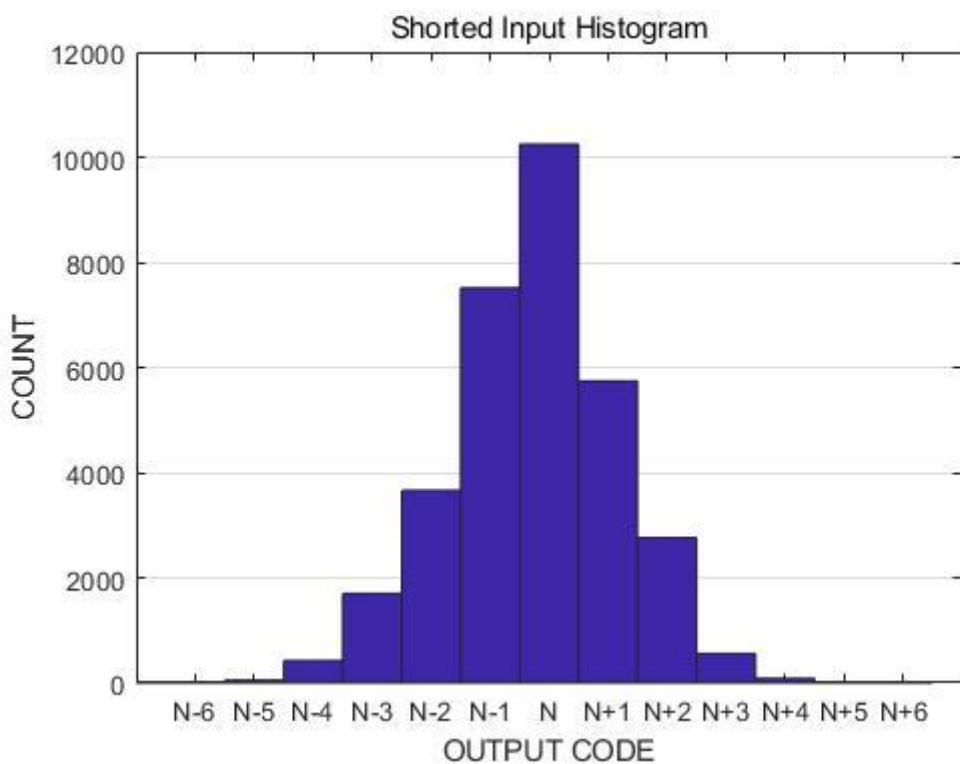

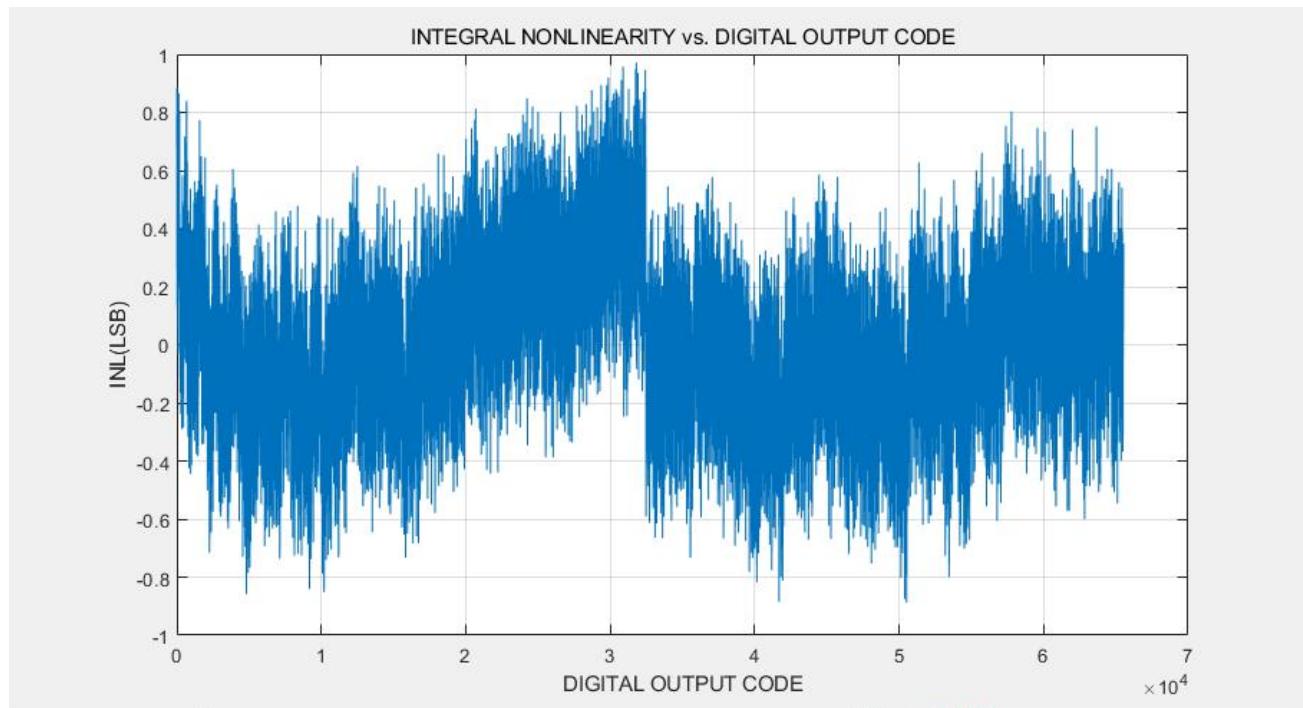

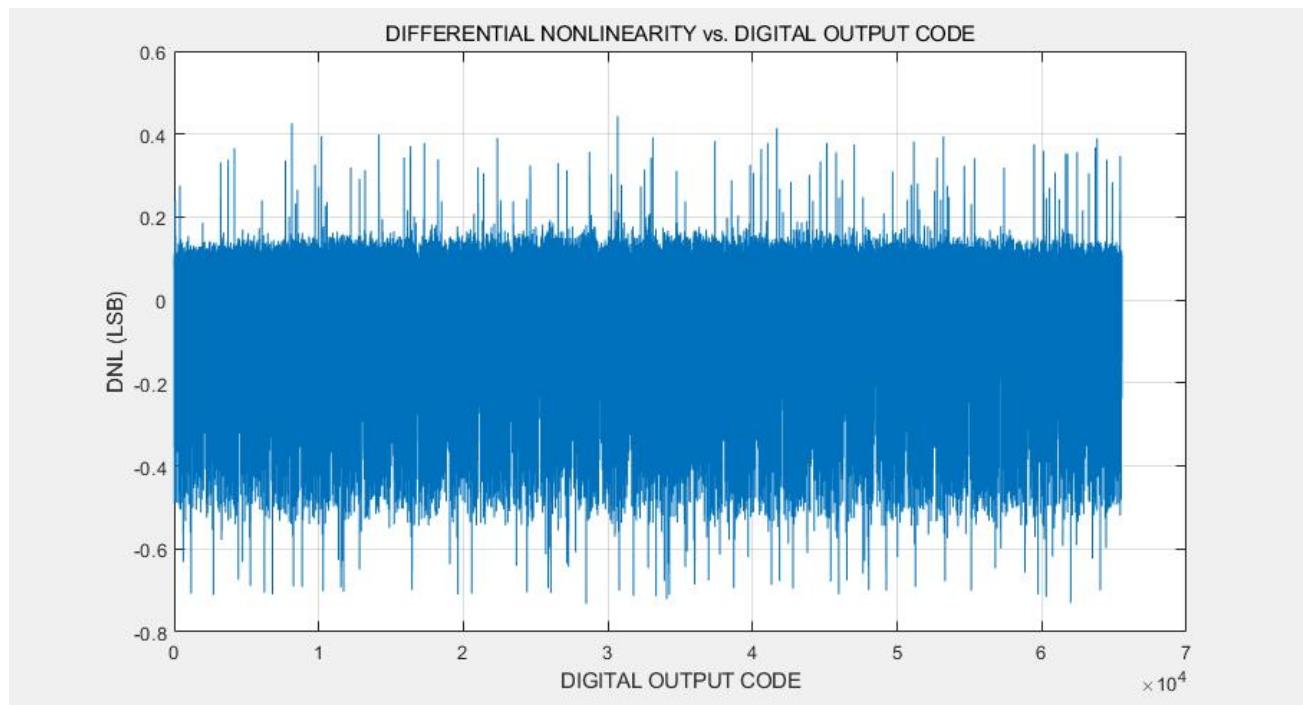

除非另有说明, AVDD=1.8V, DRVDD=1.8V, 1.0V 内部基准电压, 2Vpp 差分输入, VIN=-1.0dBFS, TA=25°C。

图 7 Fin=4.9MHz, -1dBFS, 20MSPS, 25°C

图 8 Fin=4.9MHz, -1dBFS, 20MSPS, -40°C

图 9 Fin=4.9MHz, -1dBFS, 20MSPS, 85°C

图 10 噪底直方图

16bit 20MSPS 1.8V双通道ADC

ZYL2271

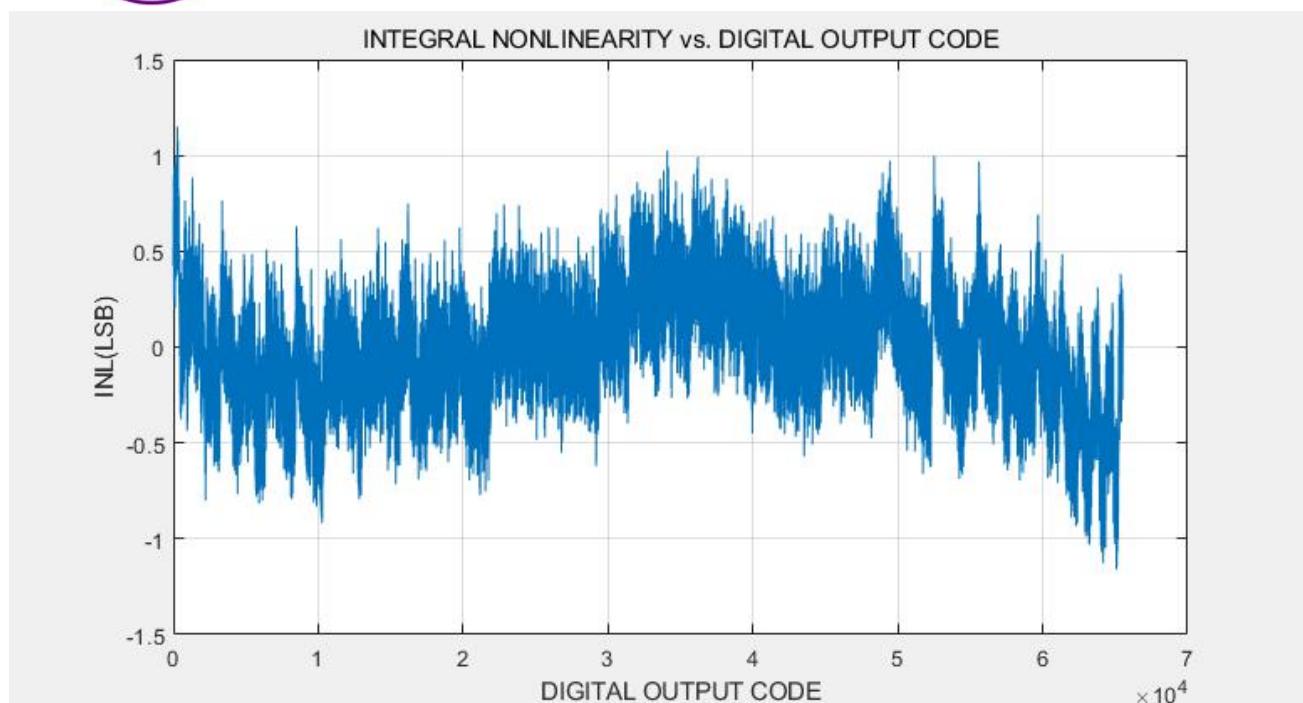

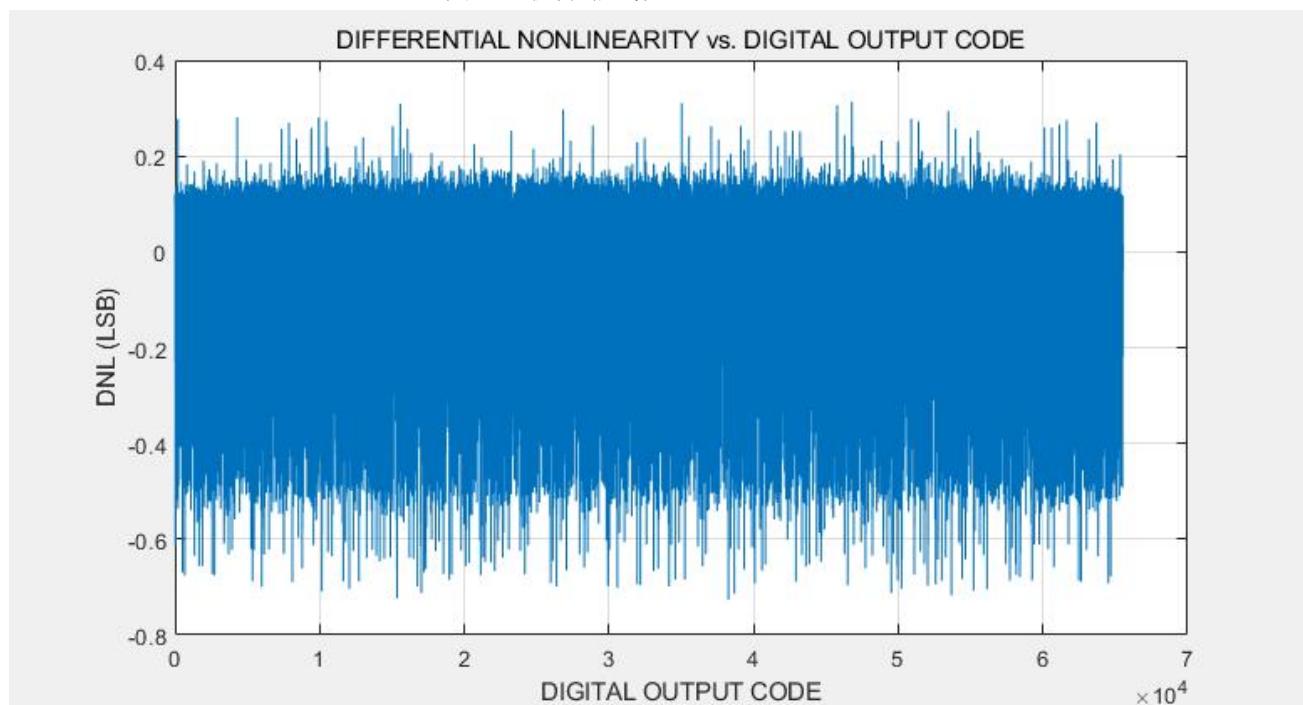

图 11 积分非线性 (INL) , 25°C

图 12 微分非线性 (DNL) , 25°C

16bit 20MSPS 1.8V双通道ADC

ZYL2271

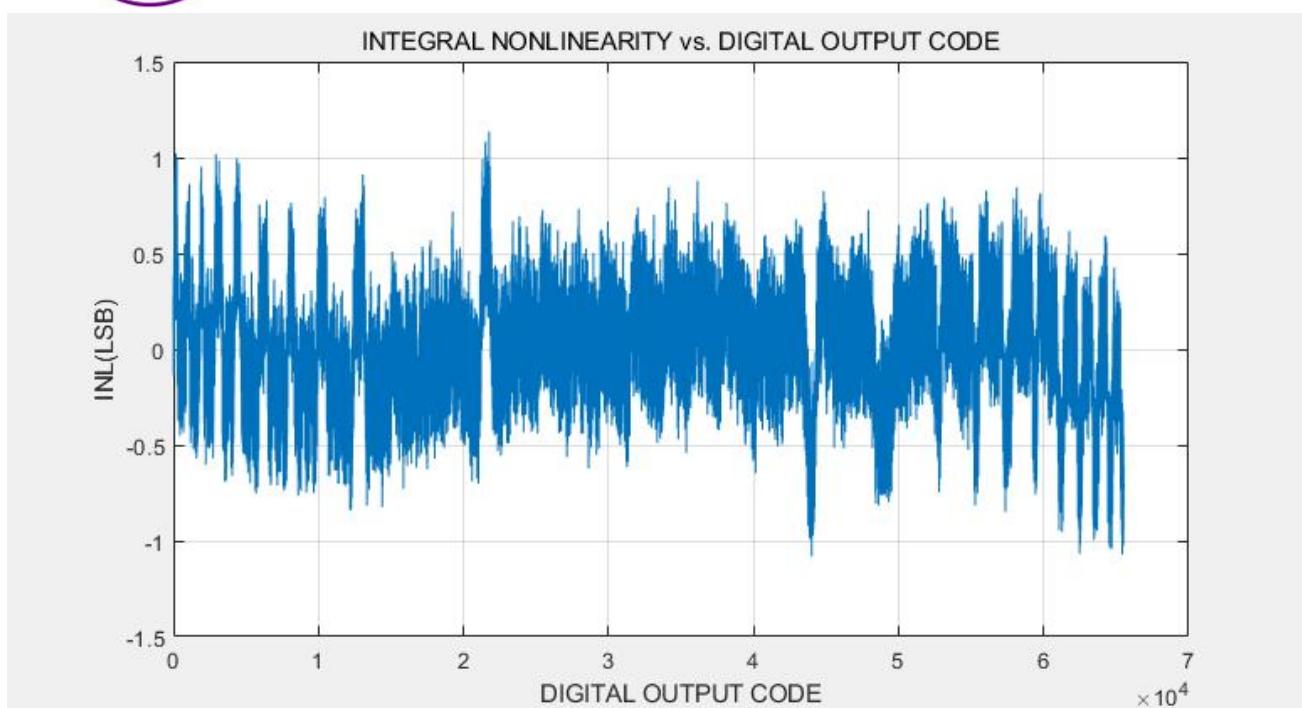

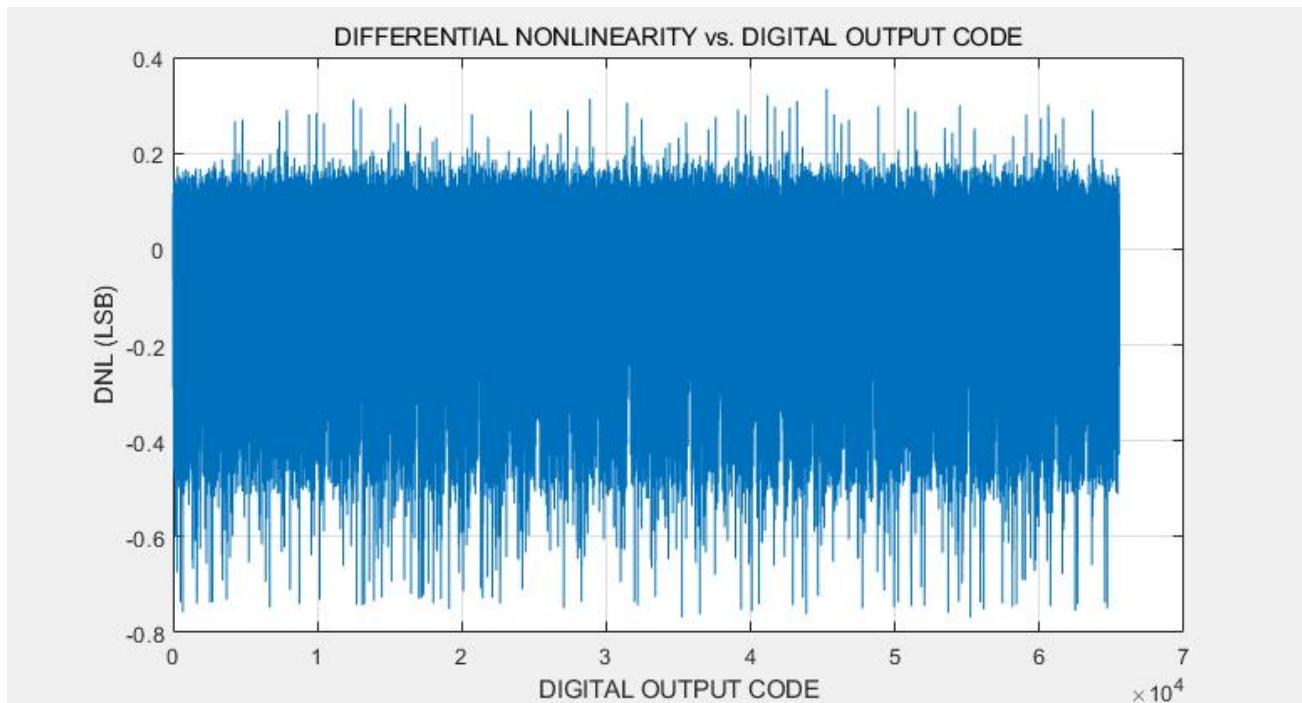

图 13 积分非线性 (INL) , -40°C

图 14 微分非线性 (DNL) , -40°C

图 15 积分非线性 (INL) , 85°C

图 16 微分非线性 (DNL) , 85°C

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 等效电路

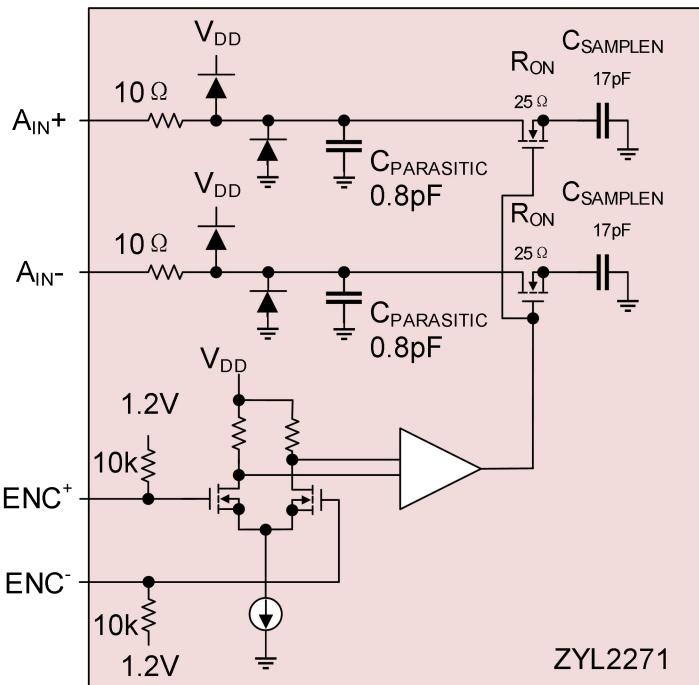

图 17 等效电路 (ZYL2271)

## 应用信息

### 转换器工作

ZYL2271 是低功率、低噪声、2 通道、16 位、20MSPS A/D 转换器，由单 1.8V 电源供电。必须对模拟输入进行差分驱动。可以对时钟输入进行差分驱动（以实现最优的抖动性能）或单端驱动（以实现较低的功耗）。数字输出为串行 LVDS，旨在最大限度地减少数据线的数目。每个通道一次输出两个位（“双线道”模式）。在较低采样速率条件下提供了每通道输出一个位的选项（“单线道”模式）。通过利用一个串行 SPI 端口设置模式控制寄存器，还可以选择许多其他的功能。

## 模拟输入

模拟输入是差分 CMOS 采样及保持电路(图 18)。应以一个由 VCM1 或 VCM2 输出引脚设定的共模电压(标称值为 1.0V)对输入进行差分驱动。对于 2V 输入范围, 输入应在 VCM - 0.5V 至 VCM + 0.5V 之间摆动。输入之间应存在 180° 的相位差。利用一个共享时钟电路对 2 个通道同时进行采样(图 18)。

图 18. 等效输入电路,只展示出了 2 个模拟通道之一

输入驱动电路

## 输入滤波

如果可能的话, 应在模拟输入端上直接布设一个 RC 低通滤波器。该低通滤波器将驱动电路与 A/D 采样及保持开关隔离开来, 而且还可遏止宽带噪声对驱动电路产生干扰。图 15 示出了输入 RC 滤波器的实例。RC 组件的参数值应根据应用电路的输入频率来选择。

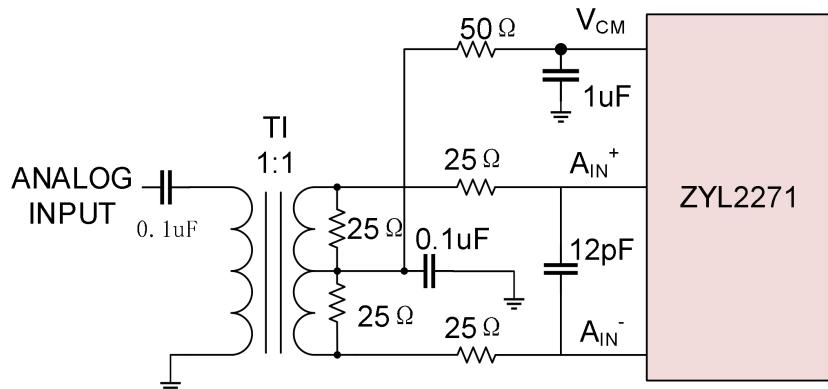

## 变压器耦合电路

图 19 示出了由一个带中心抽头副端绕组的 RF 变压器驱动的模拟输入。由 VCM 对中心抽头施加偏置, 并将 A/D 输入设定于其最佳的 DC 电平。

16bit 20MSPS 1.8V双通道ADC

ZYL2271

图 19. 采用一个变压器的模拟输入电路。推荐用于 5MHz 至 70MHz 的输入频率

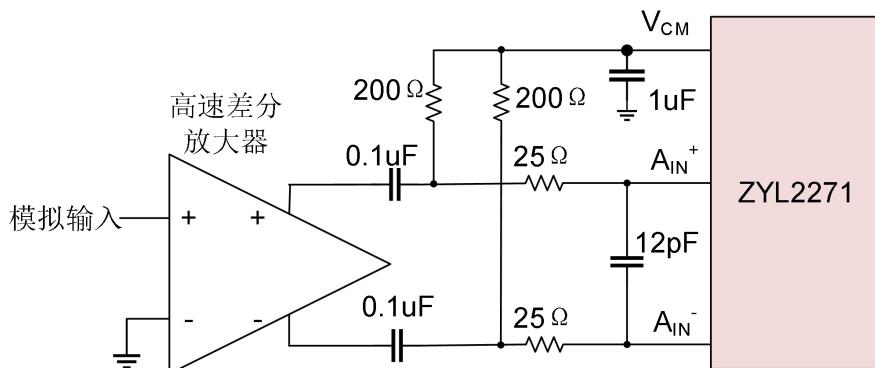

## 放大器电路

图 20 示出了由一个高速差分放大器驱动的模拟输入。放大器的输出被 AC 耦合至 A/D，因而可对放大器的输出共模电压进行最优设定以尽量降低失真。在非常高的频率下，RF 增益部件的失真常常将比差分放大器的小。

图 20. 采用一个高速差分放大器的前端电路

## 参考电平

REFH, REFL

## 时钟输入

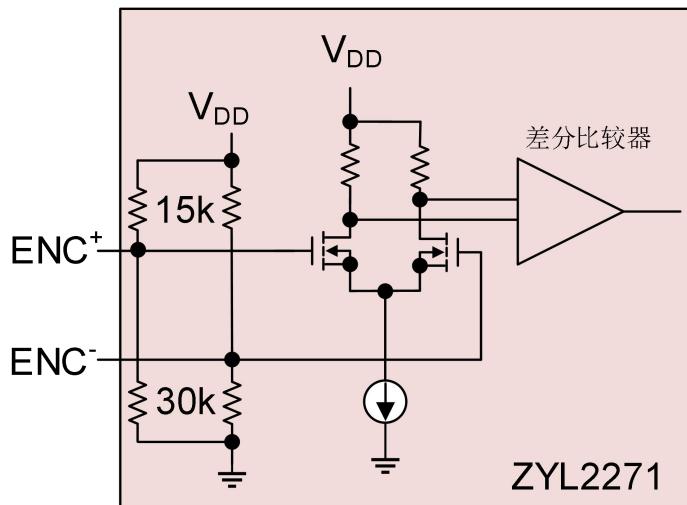

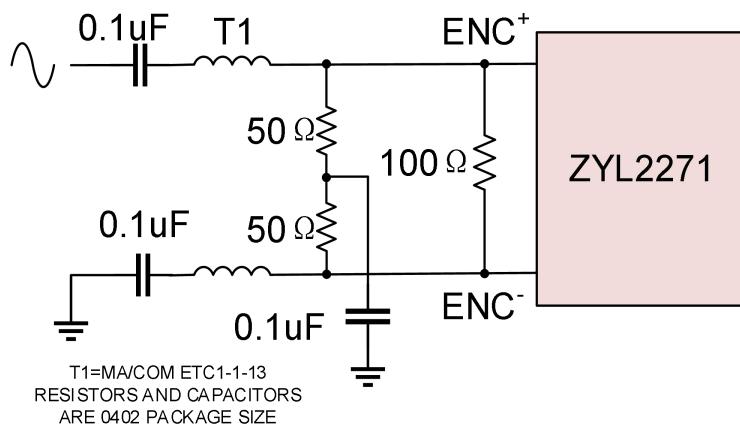

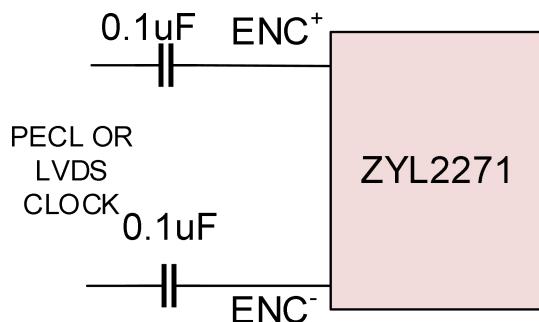

时钟输入的信号质量强烈地影响着 A/D 噪声性能。时钟输入应被视作模拟信号——其布线不要邻近电路板上的数字印制线。时钟输入有两种操作模式：差分时钟模式（图 21）和单端时钟模式（图 22）。

对于正弦、PECL 或 LVDS 时钟输入，推荐使用差分时钟模式（图 21）。通过 10k 等效电阻在内部给时钟输入施加 1.2V 偏压。时钟输入可被拉至高于 VDD（最高可至 3.6V），共模范围为 1.1V 至 1.6V。在差分时钟模式中，ENC-应至少比地电位高出 200mV，以避免错误地触发单端时钟模式。为了获得优良的抖动性能，ENC+应具有快速上升和下降时间。

16bit 20MSPS 1.8V双通道ADC

ZYL2271

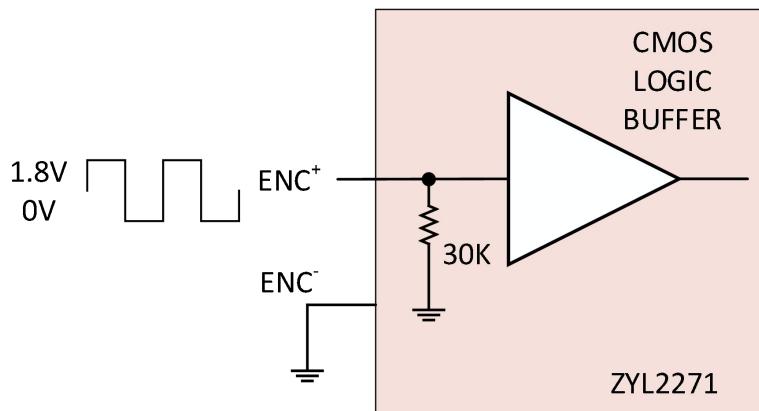

单端时钟输入模式应与 CMOS 编码输入配合使用。如欲选择该模式，则把 ENC-连接至地，并利用一个方波时钟输入驱动 ENC+。ENC+可被拉至高于 VDD (最高可至 3.6V)，因而可以使用 1.8V 至 3.3V CMOS 逻辑电平。ENC+门限为 0.9V。为了实现优良的抖动性能，ENC+应具有快速上升和下降时间。

图 21. 用于差分模式的等效时钟输入电路

图 22. 用于单端模式的等效时钟输入电路

图 23. 正弦时钟驱动

16bit 20MSPS 1.8V双通道ADC

ZYL2271

图 24. PECL 或 LVDS 时钟驱动

## 数字数据输出

ZYL2271 支持串行 LVDS 输出模式。每个通道可以通过寄存器 0x0100 配置为同时输出 2bit(2-lane 模式)或者 1bit (1-lane 模式)，具体时序见图 2、图 3。在 PCB 设计时，芯片输出的各个差分 LVDS 数据线对要尽量等长，PCB 线的阻抗控制在差分  $100\Omega$  左右。在接收端，每对差分 LVDS 数据线需要有  $100\Omega$  的端接电阻跨接在接收 BUFFER 的两个输入端之间。

ZYL2271 也支持串行 CMOS 输出模式(未开放)，具体时序见图 4、图 5。芯片只支持通过 SPI 串口配置进入 CMOS 模式，具体配置方法请联系应用工程师。

## 采样频率配置

如果采样率在 5MSPS~20MSPS 之间，芯片上电可以自动配置并工作。

如果最低采样率在 1MSPS~5MSPS 之间，需要芯片上电后通过 SPI 串口进行配置方可工作，具体配置方式请联系应用工程师。

## 输出数据格式

表 8. 输出数据格式

| 输入 (V)      | 条件 (V)            | 偏移二进制输出模式           | 二进制补码模式             |

|-------------|-------------------|---------------------|---------------------|

| VIN+ - VIN- | < -VREF - 0.5 LSB | 0000 0000 0000 0000 | 1000 0000 0000 0000 |

| VIN+ - VIN- | = -VREF           | 0000 0000 0000 0000 | 1000 0000 0000 0000 |

| VIN+ - VIN- | = 0               | 1000 0000 0000 0000 | 0000 0000 0000 0000 |

| VIN+ - VIN- | = +VREF - 1.0 LSB | 1111 1111 1111 1111 | 0111 1111 1111 1111 |

| VIN+ - VIN- | > +VREF - 0.5 LSB | 1111 1111 1111 1111 | 0111 1111 1111 1111 |

## 器件编程模式

可以利用一个并行接口或一个简单的串行接口进行设置。串行接口具有更大的灵活性，并能设置所有的可用模式。并行接口的局限性较大，只能设置某些更加常用的模式。

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 并行编程模式

使用并行编程模式，PAR/SERb 引脚必须接 VDD。在并行编程模式下，CSb, SCK, SDI 和 SDO 引脚可作为二进制逻辑输入，用于选择特定工作模式。这些引脚可以接 VDD 或地，或被 1.8V, 2.5V 及 3.3V CMOS 逻辑驱动。作为输入引脚时，SDO 应该被  $1k\Omega$  串联电阻驱动。下表列出可被 CSb, SCK, SDI 和 SDO 选通的工作模式。

表 9. 并行编程模式控制信号 (PAR/SERb=VDD)

| 引脚  | 功能                                                         |

|-----|------------------------------------------------------------|

| CSb | 2 路/1 路选择信号<br>0 = 2 路, 16 位串行输出模式<br>1 = 1 路, 16 位串行输出模式  |

| SCK | LVDS 电流选择信号<br>0 = 3.5mA LVDS 电流模式<br>1 = 1.75mA LVDS 电流模式 |

| SDI | 关机模式控制信号<br>0 = 正常工作模式<br>1 = 关机模式                         |

| SDO | 内部端接电阻选通控制信号<br>0 = 内部端接电阻断开<br>1 = 内部端接电阻使能               |

## 输出测试模式

需要测试 A/D 的数字接口时，可以采用测试模式，把所有通道的 A/D 数据输出强制为已知数值。数字输出测试模式通过配置输出模式控制寄存器 CHIPOUT5 和 CHIPOUT6 来使能。数字输出测试模式下，可分别配置 A/D 两个通道，输出测试模式包括，中间电平、最大满幅电平、最小满幅电平、长伪随机序列、短伪随机序列、上升斜坡序列、下降斜坡序列等。此外，还可以输出用户在指定寄存器中存储的电压值，A/D 两个通道分别对应 CHIPOUT7 和 CHIPOUT8，以及 CHIPOUT9 和 CHIPOUT10。

## 输出停用

可通过模式控制寄存器 CHIPOUT1 进行串行编程来停用数字输出。用于所有数字输出（包括 DCO 和 FR）的电流驱动器均被停用，以节省功率。当被停用时，每对输出的共模变至高阻抗，但差分阻抗可以保持低水平。

## 串行端口接口 (SPI)

ZYL2271 串行端口接口(SPI)允许用户利用 ADC 内部的一个结构化寄存器，来配置转换器，以满足特定功能和操作的需要。SPI 具有灵活性，可根据具体的应用进行定制。通过串行端口，可访问地址空间、对地址空间进行读写。存储空间以字节为单位进行组织，并且可以进一步细分成多个区域，如存储器映射部分所述。

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 使用 SPI 的配置

ZYL2271 的 SPI 由四部分组成：SCK 引脚、SDI 引脚、SDO 引脚和 CSb 引脚（见表 10）。SCK（串行时钟）引脚用于同步 ADC 的读出和写入数据。SDI（串行数据输入）和 SDO（串行数据输出）引脚允许将数据发送至内部 ADC 存储器映射寄存器或从寄存器中读出数据。CSb（片选信号）引脚是低电平有效控制引脚，它能够使能或禁用读写周期。

表 10. 串行端口接口引脚

| 引脚  | 功能                            |

|-----|-------------------------------|

| SCK | 串行时钟。串行移位时钟输入，用来同步串行接口的读、写操作。 |

| SDI | 串行数据输入。                       |

| SDO | 串行数据输出。                       |

| CSb | 片选信号。低电平有效控制信号，用来选通读写周期。      |

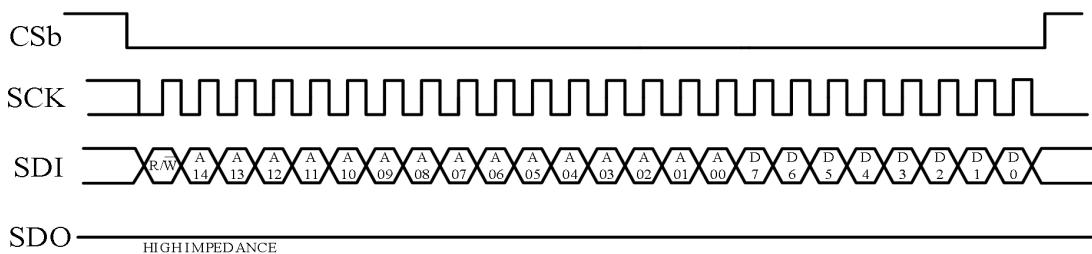

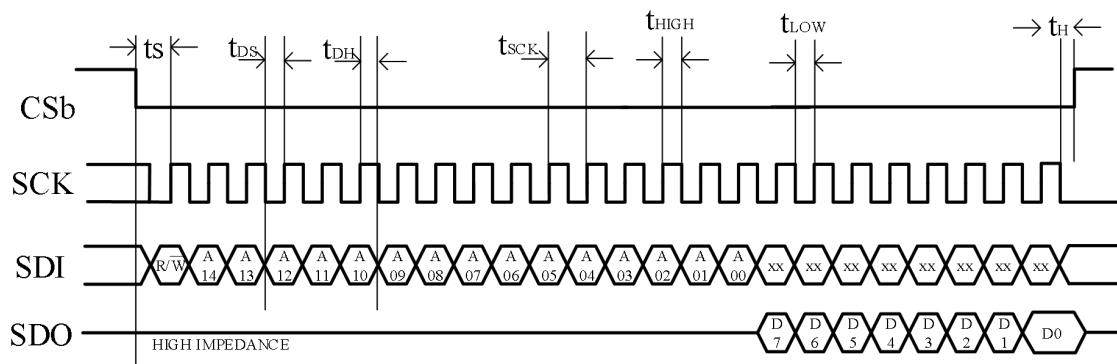

## 使用 SPI 的时序

SPI 模块是负责接收主控传来的读写指令，转换成寄存器的读写时序。

8 位数据通过一组 24 位串行字被写至一个寄存器。也可从一个寄存器读回数据以验证其内容。

串行数据传送在 CSb 被拉至低电平时起动。SDI 引脚上的数据被锁存于 SCK 的第 24 个上升沿。第 24 个上升沿之后的所有 SCK 上升沿均被忽略。当 CSb 被重新拉至高电平时，串行数据传送结束。16 位输入字的第一个位是 R/W 位。接下去的 15 个位是寄存器的地址位（A14:A0）。最后 8 位则是寄存器数据位（D7:D0）。

假如 R/W 位为低电平，那么串行数据（D7:D0）将被写至由地址位（A14:A0）设定的寄存器，如图 25 所示。倘若 R/W 位为高电平，则位于由地址位（A14:A0）设定的寄存器中的数据将在 SDO 引脚上被读回，如图 26 所示。SPI 时序如表 11 所示。

表 11.

| 参数         | 条件                  | 限值         |

|------------|---------------------|------------|

| SPI 时序要求   |                     |            |

| $t_{DS}$   | 数据与 SCLK 上升沿之间的建立时间 | 2ns (min)  |

| $t_{DH}$   | 数据与 SCLK 上升沿之间的保持时间 | 2ns (min)  |

| $t_{CLK}$  | SCLK 周期             | 40ns (min) |

| $t_s$      | CSb 与 SCLK 之间的建立时间  | 2ns (min)  |

| $t_h$      | CSb 与 SCLK 之间的保持时间  | 2ns (min)  |

| $t_{HIGH}$ | SCLK 高电平脉冲宽度        | 10ns (min) |

| $t_{LOW}$  | SCLK 低电平脉冲宽度        | 10ns (min) |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

图 25. SPI 写模式典型波形

图 26. SPI 读模式典型波形

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 存储器映射

### 存储器映射寄存器表

此器件目前不支持表 12 中未包括的所有地址和比特位。

表 12. 存储器映射寄存器

| 地址     | 寄存器名称      | Bit7<br>(MSB)      | Bit6 | Bit5          | Bit4           | Bit3              | Bit2         | Bit1           | Bit0 | 默认值  | 备注   |  |  |  |  |  |  |

|--------|------------|--------------------|------|---------------|----------------|-------------------|--------------|----------------|------|------|------|--|--|--|--|--|--|

| 0x0000 | Soft reset |                    |      | SOFT_RST0     |                |                   | SOFT_RST1    |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0001 | Vendor ID0 | 0                  | 1    | 0             | 1              | 0                 | 1            | 0              | 0    | 0x54 | “T”  |  |  |  |  |  |  |

| 0x0002 | Vendor ID1 | 0                  | 1    | 0             | 0              | 0                 | 0            | 1              | 0    | 0x42 | “B”  |  |  |  |  |  |  |

| 0x0003 | CHIP ID    | 1                  | 1    | 1             | 1              | 1                 | 1            | 0              | 0    | 0xFC |      |  |  |  |  |  |  |

| 0x0005 | UID2       | UID<23:16>         |      |               |                |                   |              |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0006 | UID1       | UID<15:8>          |      |               |                |                   |              |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0007 | UID0       | UID<7:0>           |      |               |                |                   |              |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0009 | CHIPO UT1  | CMOS_OEN           |      |               |                |                   |              |                |      |      |      |  |  |  |  |  |  |

| 0x0100 | CHIPO UT2  |                    |      |               |                | PLL_ENA_BLE       | OUTMODE<2:0> |                |      |      | 0x00 |  |  |  |  |  |  |

| 0x0107 | TPD_A DJ   | DELAY_2LANE_16BIT  |      |               |                | DELAY_1LANE_16BIT |              |                |      | 0x31 |      |  |  |  |  |  |  |

| 0x010A | CHIPO UT3  | LVDS_INTR_SEL      |      |               |                |                   |              |                |      | 0x48 |      |  |  |  |  |  |  |

| 0x010C | CHIPO UT4  |                    |      |               |                |                   |              | LVDS_SWING     |      | 0x0F |      |  |  |  |  |  |  |

| 0x0200 | CHIPO UT5  | TEST_MODE          |      | RESET_PN_LONG | RESET_PN_SHORT |                   |              | OUTPUT_FOR_MAT |      | 0x00 |      |  |  |  |  |  |  |

| 0x0201 | CHIPO UT6  | OUTPUT_TEST_MODE0  |      |               |                | OUTPUT_TEST_MODE1 |              |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0202 | CHIPO UT7  | PRESET_CODE0<15:8> |      |               |                |                   |              |                |      | 0x00 |      |  |  |  |  |  |  |

| 0x0203 | CHIPO UT8  | PRESET_CODE0<7:0>  |      |               |                |                   |              |                |      | 0x00 |      |  |  |  |  |  |  |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

|        |               |                    |      |  |

|--------|---------------|--------------------|------|--|

| 0x0204 | CHIPO<br>UT9  | PRESET_CODE1<15:8> | 0x00 |  |

| 0x0205 | CHIPO<br>UT10 | PRESET_CODE1<7:0>  | 0x00 |  |

## 1) Reg (0x0000)

| Bit | Name      | R/W | Default Value | Description                                                                                                                                    |

|-----|-----------|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 |           |     | 2'b00         | non-used                                                                                                                                       |

| 5   | SOFT_RST0 | RW  | 1'b0          | Soft reset. Should be valid when both SOFT_RST0 and SOFT_RST1 are set to 1. Users should then set these two bits to 0 to finish reset process. |

| 4:3 |           |     | 2'b00         | non-used                                                                                                                                       |

| 2   | SOFT_RST1 | RW  | 1'b0          | Soft reset. Should be valid when both SOFT_RST0 and SOFT_RST1 are set to 1. Users should then set these two bits to 0 to finish reset process. |

| 1:0 |           |     | 2'b00         | non-used                                                                                                                                       |

## 2) Reg(0x0001)

| Bit | Name            | R/W | Default Value | Description |

|-----|-----------------|-----|---------------|-------------|

| 7:0 | VENDOR_ID0<7:0> | RO  | 0x54          | ASCII “T”   |

## 3) Reg(0x0002)

| Bit | Name            | R/W | Default Value | Description |

|-----|-----------------|-----|---------------|-------------|

| 7:0 | VENDOR_ID1<7:0> | RO  | 0x42          | ASCII “B”   |

## 4) Reg(0x0003)

| Bit | Name         | R/W | Default Value | Description     |

|-----|--------------|-----|---------------|-----------------|

| 7:0 | CHIP_ID<7:0> | RO  | 0xFC          | ID for project. |

## 5) Reg(0x0005)

| Bit | Name       | R/W | Default Value | Description |

|-----|------------|-----|---------------|-------------|

| 7:0 | UID<23:16> | RO  | 0x00          | Unique ID   |

## 6) Reg(0x0006)

| Bit | Name      | R/W | Default Value | Description |

|-----|-----------|-----|---------------|-------------|

| 7:0 | UID<15:8> | RO  | 0x00          | Unique ID   |

## 7) Reg(0x0007)

| Bit | Name     | R/W | Default Value | Description |

|-----|----------|-----|---------------|-------------|

| 7:0 | UID<7:0> | RO  | 0x00          | Unique ID   |

## 8) Reg(0x0009)

| Bit | Name     | R/W | Default Value | Description                                                                           |

|-----|----------|-----|---------------|---------------------------------------------------------------------------------------|

| 7:3 | CMOS_OEN | RW  | 5'b00000      | cmos output mode enable:<br>5'b00000: cmos mode disable<br>5'b11110: cmos mode enable |

| 2:0 |          |     | 3'b000        | non-used                                                                              |

## 9) Reg(0x0100)

| Bit | Name         | R/W | Default Value | Description                                                                                                               |

|-----|--------------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------|

| 7   |              |     | 1'b0          | non-used                                                                                                                  |

| 6   |              |     | 1'b0          | non-used                                                                                                                  |

| 5:4 |              |     | 2'b00         | non-used                                                                                                                  |

| 3   | PLL_ENABLE   | RW  | 1'b0          | PLL enable bit<br>0:pll on<br>1:pll power down                                                                            |

| 2:0 | OUTMODE<2:0> | RW  | 3'b000        | Data output mode<br>3b'000:2-Lanes,16-bit serialization<br>3b'001~3b'110: Non-used<br>3b'111:1-Lanes,16-bit serialization |

## 10) Reg(0x0107)

| Bit | Name              | R/W | Default Value | Description                                                                                |

|-----|-------------------|-----|---------------|--------------------------------------------------------------------------------------------|

| 7:4 | DELAY_2LANE_16BIT | RW  | 4'b0011       | Tpd for 2LANE_16BIT mode:<br>000: -1.5Tser<br>001: 0.5Tser<br>010: 2.5Tser<br>011: 4.5Tser |

|     |                     |         |                                                                                                                                                              |                                                                |

|-----|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|     |                     |         |                                                                                                                                                              | 100: 6.5Tser<br>101: 8.5Tser<br>110: 10.5Tser<br>111: 12.5Tser |

| 3:0 | DELAY_1LANE_E_16BIT | 4'b0001 | Tpd for 1LANE_16BIT mode:<br>000: -1.5Tser<br>001: 0.5Tser<br>010: 2.5Tser<br>011: 4.5Tser<br>100: 6.5Tser<br>101: 8.5Tser<br>110: 10.5Tser<br>111: 12.5Tser |                                                                |

## 11) Reg(0x010A)

| Bit | Name          | R/W | Default Value | Description                                                      |

|-----|---------------|-----|---------------|------------------------------------------------------------------|

| 7   | LVDS_INTR_SEL | RW  | 1'b0          | LVDS internal 100-ohm load selection:<br>0: disable<br>1: enable |

| 6:0 |               |     | 0x48          | non-used                                                         |

## 12) Reg(0x010C)

| Bit | Name       | R/W | Default Value | Description                                                     |

|-----|------------|-----|---------------|-----------------------------------------------------------------|

| 7:2 |            |     | 6'b0000<br>11 | non-used                                                        |

| 1   | LVDS_SWING | RW  | 1'b1          | Swing contrl in LVDS mode.<br>0: low-swing mode<br>1: ANSI mode |

| 0   |            |     | 1'b1          | non-used                                                        |

## 13) Reg(0x0200)

| Bit | Name      | R/W | Default Value | Description                                                                                                                                                |

|-----|-----------|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TEST_MODE | RW  | 1'b0          | Test mode enable:<br>0: normal mode<br>1: test mode<br>Should be sync to clk_main domain.<br>Should be set after OUTPUT_TEST_MODE and PRESET_CODE are set. |

|     |                |    |       |                                                                                                         |

|-----|----------------|----|-------|---------------------------------------------------------------------------------------------------------|

| 6   |                |    | 1'b0  | Non-used                                                                                                |

| 5   | RESET_PN_LONG  | RW | 1'b0  | Reset long PN generator, high active. Should be sync to clk_main domain.<br>0: non-reset<br>1: reset    |

| 4   | RESET_PN_SHORT | RW | 1'b0  | Reset short PN generator, high active. Should be sync to clk_main domain.<br>0: non-reset<br>1: reset   |

| 3:2 |                |    | 2'b00 | Non-used                                                                                                |

| 1:0 | OUTPUT_FORMAT  | RW | 2'b00 | Output format:<br>2'b00: offset binary<br>2'b01: twos complement<br>2'b10: gray code<br>2'b11: reserved |

#### 14) Reg(0x0201)

| Bit | Name               | R/W | Default Value | Description                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | OUTPUT_TES_T_MODE0 | RW  | 0x00          | Output Test mode for ADC Core0:<br>0000: off<br>0001: 0x7FFF<br>0010: negative FS<br>0011: positive FS<br>0101: PN long sequence. Please refer PN23 in ITU-T 0.150<br>0110: PN short sequence. Please refer PN9 in ITU-T 0.150<br>1000: Reverse value of preset code in reg 0x02 & reg 0x03<br>1001: ramp-down output<br>1010: ramp-up output<br>Others: reserved |

| 3:0 | OUTPUT_TES_T_MODE1 | RW  | 0x00          | Output Test mode for ADC Core1:<br>0000: off<br>0001: mid scale<br>0010: positive FS<br>0011: negative FS<br>0101: PN long sequence. Please refer PN23 in ITU-T 0.150<br>0110: PN short sequence. Please refer PN9 in ITU-T 0.150<br>1000: preset code in reg 0x04 & reg 0x05<br>1001: ramp-up output<br>1010: ramp-down output<br>Others: reserved.              |

## 15) Reg(0x0202)

| Bit | Name                   | R/W | Default Value | Description                                 |

|-----|------------------------|-----|---------------|---------------------------------------------|

| 7:0 | PRESET_COD<br>E0<15:8> | RW  | 0x00          | Preset code when OUTPUT_TEST_MODE0=4'b1000; |

## 16) Reg(0x0203)

| Bit | Name                  | R/W | Default Value | Description                                 |

|-----|-----------------------|-----|---------------|---------------------------------------------|

| 7:0 | PRESET_COD<br>E0<7:0> | RW  | 0x00          | Preset code when OUTPUT_TEST_MODE0=4'b1000; |

## 17) Reg(0x0204)

| Bit | Name                   | R/W | Default Value | Description                                 |

|-----|------------------------|-----|---------------|---------------------------------------------|

| 7:0 | PRESET_COD<br>E1<15:8> | RW  | 0x00          | Preset code when OUTPUT_TEST_MODE1=4'b1000; |

## 18) Reg(0x0205)

| Bit | Name                  | R/W | Default Value | Description                                 |

|-----|-----------------------|-----|---------------|---------------------------------------------|

| 7:0 | PRESET_COD<br>E1<7:0> | RW  | 0x00          | Preset code when OUTPUT_TEST_MODE1=4'b1000; |

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 应用信息

### 设计指南

在进行 ZYL2271 的系统设计和布局之前，建议设计者先熟悉下述设计指南，其中讨论了某些引脚所需的特殊电路连接和布局布线要求。设计前请联系申请 FAQ。

### 电源和接地建议

建议使用两个独立的 1.8V 电源为 ZYL2271 供电：一个用于模拟端 (AVDD)，一个用于数字输出端 (DRVDD)。对于 AVDD 和 DRVDD，应使用多个不同的去耦电容以应对高频和低频。去耦电容应放置在接近 PCB 入口点和接近器件引脚的位置，并尽可能缩短走线长度。

ZYL2271 仅需要一个 PCB 接地层。对 PCB 模拟、数字和时钟模块进行合理的去耦和巧妙的分隔，可以轻松获得最佳性能。

### 裸露焊盘散热块建议

为获得最佳的电气性能和热性能，必须将 ADC 底部的裸露焊盘连接至模拟地 (GND)。PCB 上裸露 (无阻焊膜) 的连续铜平面应与 ZYL2271 的裸露焊盘 (引脚 53) 匹配。

铜平面上应有多个通孔，以便获得尽可能低的热阻路径以通过 PCB 底部进行散热。应当填充或阻塞这些通孔，防止通孔渗锡而影响连接性能。

为了最大化地实现 ADC 与 PCB 之间的覆盖与连接，应在 PCB 上覆盖一个丝印层，以便将 PCB 上的连续平面划分为多个均等的部分。这样，在回流焊过程中，可在 ADC 与 PCB 之间提供多个连接点。而一个连续的、无分隔的平面则仅可保证在 ADC 和 PCB 之间有一个连接点。

### VCM

VCM 引脚应通过一个 0.1uF 电容去耦至地。

### 基准电压源去耦

VREF 引脚应通过外部一个低 ESR 的 1.0  $\mu$ F 电容去耦至地。

### SPI 端口

当需要转换器充分发挥其全动态性能时，应禁用 SPI 端口。通常 SCK 信号、CSb 信号、SDI 信号和 SDO 信号与 ADC 时钟是异步的，因此，这些信号中的噪声会降低转换器性能。如果其他器件使用板上 SPI 总线，则可能需要在该总线与 ZYL2271 之间连接缓冲器，以防止这些信号在关键的采样周期内，在转换器输入端发生变化。

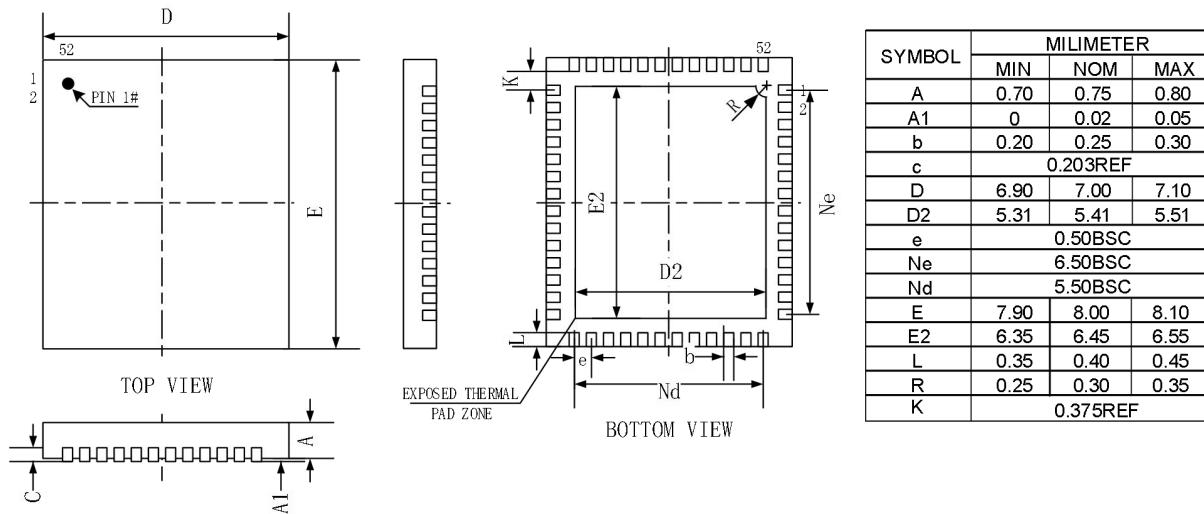

## 外形尺寸

图 27. 封装尺寸 QFN52 (7mm x 8mm)

16bit 20MSPS 1.8V双通道ADC

ZYL2271

## 名词对照表

|      |                  |

|------|------------------|

| 通道   | channel          |

| 线道   | lane             |

| 转换噪声 | transition noise |

| 共模   | common mode      |

|      |                  |